Xilinx WebPACK ISE

Авторы: ФРЕНКЕЛЬ Борис Семенович, КУЗЬМИЧ Максим Сергеевич

Программируемые логические интегральные схемы (ПЛИС) представляют собой одно из самых интересных и быстроразвивающихся направлений современной цифровой микроэлектроники. За последнее десятилетие наблюдался бурный рост рынка этих устройств и существенное улучшение их характеристик. Прогнозы в этой области на ближайшее время представляются самыми оптимистичными.

С появлением ПЛИС проектирование цифровых микросхем перестало быть уделом исключительно крупных предприятий с объёмами выпуска в десятки и сотни тысяч кристаллов. Проектирование и выпуск небольшой партии уникальных цифровых устройств стал возможен в условиях проектно-конструкторских подразделений промышленных предприятий, в исследовательских и учебных лабораториях и даже в условиях домашних радиолюбительских рабочих мест. Промышленно выпускаемые "заготовки" программируемых микросхем с электрическим программированием и автоматизированным процессом перевода схемы пользователя в последовательность импульсов программирования делают проектирование новых цифровых устройств сравнимым с разработкой программного обеспечения.

Курс лабораторных работ по дисциплине "Технические средства микропроцессорных систем", посвящённый проектированию цифровых систем на базе ПЛИС на языке VHDL, призван познакомить студентов с современной методикой проектирования микроэлектронных систем. Выполнение данных лабораторных работ поможет в получении необходимой базовой подготовки для дальнейшей работы в качестве инженера по разработке и обслуживанию современных микроэлектронных систем.

ВОПРОСЫ ДЛЯ САМОСТОЯТЕЛЬНОЙ ПОДГОТОВКИ

[править]1. Ввести имена входов и выходов схемы с использованием типа BIT_VECTOR. 2. Составить VHDL-модель каждого из типов элементов, входящих в схему. 3. Составить иерархическое VHDL-модель схемы в целом для конкретного значения N (обычно N=4). 4. Написать тестирующую программу и провести моделирование иерархического описания, получить временную диаграмму. 5. Провести описание регулярной схемы с использованием операторов generate, generic для произвольной разрядности N. 6. Написать тестирующую программу для моделирования по способу 2 при том же значении выбранного в п. 3 параметра N. 7. Сравнить результаты моделирования по способу 1 и способу 2 (результаты должны быть одинаковыми).

Изучение ПЛИС с архитектурой FPGA

[править]Архитектура ПЛИС фирмы Xilinx. Топология ПЛИС. Логическая таблица. Триггер. Структура конфигурируемого логического блока. Схемы для ускорения арифметических операций. Мультиплексоры в ПЛИС. Шины с тремя состояниями. ОЗУ в ПЛИС. Блоки ввода-вывода сигналов. Система синхронизации. Конфигурирование ПЛИС [2, 9, 11].

ПЛИС семейства Virtex. Особенности архитектуры. Матрица Virtex. Архитектурные особенности структурных блоков. Блочная память. Программируемая трассировочная матрица. Распределение сигналов синхронизации. Периферийное сканирование. Режимы конфигурирования кристалла. Обозначения микросхем [2, 11].

ПЛИС семейства Spartan-3. Особенности архитектуры. Матрицы Spartan-3 и Spartan-3E. Архитектурные особенности структурных блоков. Передача данных с удвоенной скоростью. Цифровое управление импедансом. Блоки умножителей. Цифровой блок управления синхронизацией (DCM). Временные параметры и обозначения микросхем [2, 5, 7, 11].

Изучение средств управления проектированием

[править]Технология разработки систем на кристалле. Вычислительные заготовки.

Особенности языка VHDL для синтеза и анализа. Методы организации системы синхронизации. Однотактная синхронизация. Двухтактная синхронизация. Временной анализ проектов микросхем. Анализ потребляемой мощности [1, 3, 4, 9, 11].

Программное обеспечение для проектирования систем на базе ПЛИС. САПР WebPACK ISE. Система HDL-моделирования ModelSim XE Starter Edition.

Этапы проектирования в САПР WebPACK ISE. Создание модулей исходного описания проектируемого устройства. Синтез проектов, реализуемых на базе ПЛИС семейств FPGA фирмы Xilinx. Реализация проектов на базе ПЛИС семейств FPGA фирмы Xilinx. Моделирование цифровых устройств. Конфигурирование и оценка потребляемой мощности цифровых устройств, проектируемых на базе ПЛИС фирмы Xilinx [1].

WEBPACK ISE – СРЕДСТВО ПРОЕКТИРОВАНИЯ ЦИФРОВЫХ УСТРОЙСТВ

[править]Начало работы с системой

[править]Для запуска САПР WebPACK ISE необходимо выполнить двойной щелчок мышью на иконке, расположенной на рабочем столе:

Xilinx ISE 8.1i

Другим способом запуска является выбор в главном меню операционной системы пункта "ПУСК" → "Программы" → "Xilinx ISE 8.1i" → "Project Navigator".

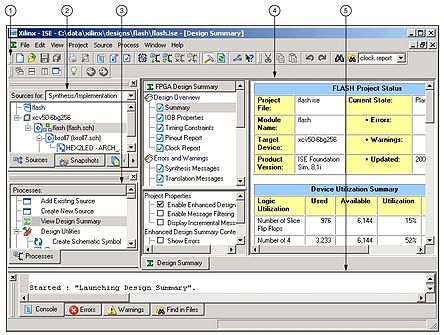

В результате будет запущен "Навигатор проекта" ("Project Navigator") – основная программа САПР WebPACK ISE. "Навигатор проекта" позволяет упорядочить файлы с исходным описанием проектируемого устройства, тестовыми модулями, модулями временных и топологических ограничений, а также предоставляет возможность простого доступа ко всем процессам, необходимым при проектировании цифрового устройства на базе ПЛИС с архитектурами FPGA и CPLD. На рисунке 1 показан внешний вид основного окна Навигатора проекта и его компоненты.

Каждому из этих этапов соответствует определённый набор процессов, к которым можно получить доступ из "Навигатора проектов".

Во время работы с САПР WebPACK ISE по всем необходимым вопросам рекомендуется обращаться к справочной системе самого ISE и сопутствующих продуктов. Для доступа к справочной системе достаточно нажать клавишу F1, что даст возможность получения контекстно-зависимой справки по выполняемой в настоящий момент задаче. Если необходимо получить доступ к определённому разделу справочной системы, то можно воспользоваться пунктом меню "Help" (рисунок 2).

При наличии подключения к Интернету из этого же раздела меню можно получить доступ к различным справочным и учебным материалам на сайте компании Xilinx (http://www.xilinx.com(англ.)), а также обновить текущую версию САПР WebPACK ISE.

1. Создание проекта в Webpack ISE 11.1 Запустим Webpack ISE 11.1, щелкнув мышью по иконке Xilinx ISE 11 на рабочем столе. Запустится окно ISE Project navigator программы Webpack ISE 11.1. Закроем предыдущий проект, выбрав File->Close Project. Закроется предыдущий проект и откроется панель Getting Started с надписью No project is open и четырьмя кнопками, из которых нажмем на New Project. Запустится New Project Wizard с панелью Create New Project (рисунок 1). Рисунок 1 На панели Enter a name, locations and comment for the project в поле Location нажать на кнопку с тремя точками. Откроется окно Обзор папок, с помощью которого выбрать или создать папку где будет храниться проект. В нашем случае выберем диск D и нажмем на кнопку создать папку. Появится новая папка, в поле имени которой введем New_Xilinx_Projects и нажмем на кнопку Ok окна Обзор папок. В окне New Project Wizard в поле Location появится путь к созданной папке D:\New_Xilinx_Projects\. В поле Name введем имя проекта 2st_counter. В поле Description введем короткий текст описания проекта примерно такого содержания «Пробный проект на базе двухразрядного счетчика, показывающий основные этапы проектирования в пакете Webpack ISE 11.1». В этом же окне ниже в панели Select the type of top-level source for the project в списке Top-level source type выберем тип источника верхнего уровня как Schematic. После этого нажмем на кнопку Next. Откроется следующий шаг под названием Device Properties мастера New Project Wizard, где на панели Select the device and project properties выпадающие списки, с помощью настраиваются тип платформы ПЛИС, способы задания файлов верхнего уровня иерархии и т. д.. Даная вкладка устанавливает свойства конфигурацию микросхемы, на базе которой будет создано устройство (рисунок 2). Рассмотрим этот этап по подробнее.

Рисунок 2

В списке Product Category можно выбрать назначение продукта, напри-мер, General Purpose, Military и т. д. Это не принципиально, поэтому оставим значение этого поля по умолчанию как All.

В списке Family выберем семейство микросхем Virtex-5.

В списке Device выберем микросхему XC5VSX35T.

В списке Package выберем тип корпуса FF665.

В списке Speed выберем скорость 1.

В списке Top-level source type по умолчанию стоит значение Schematic, выбранное нами на предыдущей стадии.

В списке Synthesis Tool выберем XST (VHDL/Verilog).

В списке Simulator выберем тип симулятора ISim (VHDL/Verilog). Здесь следует отметить, что этот список имеет большое количество используемых симуляторов VHDL и Verilog, которые могут использоваться для моделирования проекта. Наиболее распространенным симулятором является ModelSim фирмы Mentor Graphics. В данном пакете могут использоваться симуляторы от ModelSim 6.4b и более новых версий. Мы в нашем примере используем встроенный VHDL симулятор ISim.

В списке Preferred Language выберем основной язык описания аппара-туры VHDL. Остальные списки не принципиальны. Нажмем на кнопку Next.

Откроется новый этап Create New Source мастера New Project Wizard (рисунок 3), позволяющий создать источник схемы или кода. Пропустим этот этап нажав на Next.

Рисунок 3 Следующий этап мастера New Project Wizard это похожий по содержа-нию на предыдущий этап, называется Add Existing Sources (рисунок 4), позволяющий подключать уже готовые необходимые источники кода. Пропустим также и этот этап, нажав на Next. . Рисунок 4 После нажатия на Next появится окно результатов создания проекта project Summary, с помощью которого можно проверить проект и при необходимости вернуться назад, используя кнопки Back, чтобы что-либо поменять (рисунок 5). Нажмем на Finish. С закрытием мастера New Project Wizard откроется ISE Project navigator программы Webpack ISE 11.1 с созданным проектом (рисунок 6). Теперь можно приступать непосредственно к проектированию счетчика.

Рисунок 5

Рисунок 6

(более подробно работа с ISE WebPack 13.2 описана здесь)

Создание описания устройства

[править]-

Создание схемного описания устройства

-

Выбор раздела schematic

Выбираем пункт меню File/New Project и вводим имя нового проекта. Project Wizard автоматически формирует новую паку в рабочей области, выбранной при установке проекта. Устройство в Xilinx WebPack ISE может быть описано с использованием различных средств: встроенного редактора схем (schematic), языков моделирования VHDL и Verylog и др.

- В начале рассмотрим процесс создания описания устройства с помощью встроенного редактора схем. На практике в большинстве систем именно этот способ используется для создания описаний верхнего уровня.

В разделе “Top level source type” выбираем тип «Schematic». Нажимаем кнопку «Next». На следующем шаге мы должны выбрать тип ПЛИС, язык описания внутрисхемных решений и т.п. Назначить тип микросхемы и конкретные номера ножек для входов и выходов очень важно, если в конечном счете вы собираетесь зашить проект в чип CPLD или загрузить в FPGA. Если мы собираемся провести просто логическую симуляцию, то нам все равно на какой микросхеме это делать. Изменить свойства проекта можно практически в любой момент, поэтому мы пропускаем данный шаг и нажимаем кнопку Next. Завершаем создание проекта кнопкой Finish. Теперь приступим к созданию схемы. В окне Design/Hierarchi находим имя нашего проекта и с помощью контекстного меню (нажатие правой кнопки мыши) выбираем пункт New Source.

Выбираем тип файла Schematic и вводим имя файла схемы, например “double_level”. Переходим к следующему шагу и заканчиваем создание проекта нажатием кнопки «Finish». После этого будет создано окно, позволяющее нарисовать схему с использованием графических примитивов. Для первого знакомства мы будем использовать примитивы логических элементов, порты ввода/вывода (входы и выходы схемы) и проводники. Для добавления элемента схемы, в общем случае, можно использовать контекстное меню Add\Symbol или кнопку на панели инструментов. Выбираем раздел «Logic» и в списке элементов отмечаем «inv» - инвертор. В двухуровневой схеме четыре инвертора – расставляем их в редакторе.

После установки входов и выходов поименуем их – клик правой кнопки мыши на элементе и выбираем пункт меню Object Properties. Меняем имя элемента на соответствующий схеме.В идеологии Xilinx в схеме не может быть «висячих» входов и выходов, то есть не присоединенных ни к входам ни к выходам элементов. Поэтому, только после установки элемента (например,инверторов) мы можем обозначить на схеме входные порты, которые позже будут соответствовать ножкам ПЛИС. Для установки портов используем пункт контекстного меню «Add/IO marker» или одноименную кнопку на панели инструментов. Изображение порта надо совместить мышью его изображение со входом инвертора. После установки меняем имя, созданное по умолчанию, на X1..X4 соответственно. После этого добавляем в схему логические элементы типа «И-Не», используя для этого пункт меню (кнопку) «Add/Symbol», раздел «Logic», элементы nand2, nand3 и nand4 (nand – "not and", а цифра обозначает число входов). Для соединения портов, выходов инверторов и входов логических элементов используем пункт меню или кнопку «Add/Wire». Соединение может происходить в автоматическом режиме, если выводы элементов расположены на схеме рядом. В этом случае просто выделяем левой кнопкой мыши выход одного элемента и тянем соединение ко входу другого.

-

Вставка элементов в редакторе схем

-

Добавление цепи в автоматическом режиме

-

"Вид снаружи" и "виды изнутри" при описании устройства

Добавить цепь (wire) в автоматическом режиме не всегда возможно, поэтому устанавливаем переключатель в разделе «Add Wire Option» в положение «Use the Manual method…». В этом случае цепь визуально будет проводится между точками, отмечаемыми левой кнопкой мыши. Обратите внимание, что маркеры начала и конца цепи не могут находиться в области элементов или надписей. После того, как цепь создана рекомендуется сразу давать ей логически правильное название с помощью пункта контекстного меню Object Properties или “Rename Selected net”. После соединения портов и выводов элементов необходимо сохранить графический файл.

Процесс описания устройства в виде модуля на языке VHDL рассмотрим на примере создания схемного элемента, выполняющего некоторую логическую функцию. Описание на языке VHDL определяет внешние связи устройства (“вид снаружи” или интерфейс) и один или несколько “видов изнутри” . Вид снаружи задает интерфейс устройства, набор сигналов, которыми устройство обменивается с внешним миром. Этот вид описывает абстрактное представление устройства “в целом” и обозначается английским термином entity, что в дословном переводе означает «сущность» и наиболее точно отражает смысл представления.

Вид изнутри определяет функциональные возможности устройства или его структуру. Внутреннее строение объекта определяет архитектура (architecture body). Очевидно, что при описании модели устройства в первую очередь следует посмотреть на него со стороны (“вид снаружи”) и для этого “черного ящика” определить интерфейс с внешним миром. Такая задача решается в VHDL декларацией интерфейса entity. Она задает имя описания, имена интерфейсных портов, направление передачи, тип портов. Порт – это сигнальная линия (шина), с помощью которой устройство (модель) взаимодействуют с окружающей средой. Например, для описания устройства, реализующего логическую функцию вида у=(x1^x2)|~(x3^x4) (использована нотация записи выражений языка C) декларация будет выглядеть следующим образом:

entity MyF1 is Port ( x1 : in STD_LOGIC; x2 : in STD_LOGIC; x3 : in STD_LOGIC; x4 : in STD_LOGIC; f2 : out STD_LOGIC); end MyF2;

Архитектура (architecture body) моделирует взгляд на устройство “изнутри”. Архитектура имеет свое имя, например struct или behave. О принадлежности архитектуры к описанию интерфейса MyF1 говорит выражение вида «of MyF1» после имени архитектуры. Устройство может рассматриваться под разными углами и описываться по-разному. Оно может предстать либо как композиция более простых модулей (структурный стиль моделирования), либо как набор параллельно исполняемых алгоритмов (стиль dataflow), либо описано как процесс последовательного исполнения операций (стиль “поведенческий”), либо может быть раскрыто сочетанием указанных стилей. В начале рассмотрим структурный стиль, который очень близок к «схемному» решению. Структурное описание интерпретирует устройство как набор компонентов, связанных между собой сигналами или соединениями (netlist).

-- объявление компонента xnor2 architecture Struct of MyF1 is component xnor2 port (In1,In2: in STD_LOGIC; Out1: out STD_LOGIC); end component;

-- объявление компонента xor2 component xor2 port (In1,In2: in STD_LOGIC; Out1: out STD_LOGIC); end component;

-- объявление компонента or2

component or2 port (In1,In2: in STD_LOGIC; Out1: out STD_LOGIC); end component;

signal s1,s2: STD_LOGIC; --сигналы внутри схемы begin N1: XNOR2 port map ( x1, x2, s1); -- выражение 1 N2: XOR2 port map (x3, x4, s2); -- выражение 2 N3: OR2 port map (s1, s2, f2); -- выражение 2 end Struct;

Описание функционирования компонентов xnor2, xor2, or2 находится в библиотеках FPGA. Объявление компонента делает его видимым внутри нашей архитектуры. При разработке «поведенческого описания» функционирование устройства рассматривается как процесс последовательного вычисления выражений, входящих в process. Толчком к запуску процесса является изменение (event -событие) какого либо сигнала, из входящих в список “воспринимаемых” сигналов (sensitivity list). Этот список внешне очень похож на список параметров в других языках высокого уровня. Для описания комбинационной логики язык VHDL предлагает набор из шести операций: and, or, nand, nor, xor, xnor. К отдельному виду относят операцию not. Для однозначной интерпретации при записи выражений рекомендуется использовать скобки. Для ассоциации сигналов на выходе устройства или внутри его с результатом выражения используется оператор назначения сигнала (<=).

architecture behave of MyF1 is begin process (x1, x2, x3, x4) begin

- y<=(x1 xor x2) or (x3 xnor x4);

end process; end behave;

Пример создания описания комбинационной схемы и цифрового автомата в среде Xilinx WebPACK ISE приводится здесь

Тестовые модули и функциональное моделирование

[править]Использование временных ограничений

[править]Реализация устройства на базе ПЛИС

[править]Переразмещение проекта и проверка соответствия выводов

[править]Проверка проекта способом временного моделирования

[править]В этом, шестом по счету видеоуроке на сайте LOGWAYS.RU мы научимся основам работы в HDL-симуляторе ISim, который входит в пакет программ XILINX ISE Webpack 13.2. Итак, открывает ярлык на рабочем столе Xilinx ISE Design Suite 13.2. В окне Design в панели View ставим метку напротив строки Simulation.

В окне Hierarchy выбираем элемент antitwit_nofix.vhd. В окне Processes выполняем предварительную проверку синтаксиса, выбрав команду Behavioral Check Syntax. После успешной проверки синтаксиса запускаем команду Simulate Behavioral Model.

Перед нами – основное окно программы ISim. Здесь в окне Objects нам необходимо указать типы входных воздействий (т.е. какими будут наши входные сигналы). Для этого в контекстном меню входного порта INSIG выбираем команду Force Clock. Если у нас период сигнала начинается с единицы, то в поле Leading Edge Value указываем значение ‘1’, а в поле Trailing Edge Value – ‘0’. Если очередной период начинается с нуля, то наоборот.

В полях Starting at Time Offset и Cancel after Time Offset можно указать величину сдвига в начале периода сигнала относительно начала процесса симуляции и соответственно конца периода сигнала. Мы указываем нулевые сдвиги.

В поле Duty Cycle (%) указываем скважность сигнала (а скважность, как известно, это отношение длительности импульса к его периоду). Мы укажем величину 5 %.

И наконец, в поле Period указываем период входного сигнала INSIG. Напоминаю, что сигнал INSIG, это входной сигнал с флуктуациями от дребезга контактов. Эти флуктуации нам и нужно устранить. Укажем период сигнала, равным, например, 1 секунде (1s).

Кстати, в программе ISim все временные величины, если не указана размерность, выражены в пикосекундах. Если мы хотим иную размерность, то так указываем: 10s, 56ms, 3.4us, 467ns.

Точно таким же образом указываем параметры входного сигнала для порта N1kHz. В поле Period, соответственно, указываем величину 1ms.

Далее, необходимо указать время симуляции в поле рядом с кнопкой Run (синий треугольник с песочными часами). Укажем время симуляции 10 секунд (10s). После этого запускаем симуляцию, нажав кнопку Run.

После окончания симуляции возникнет необходимость просмотра всей временной области сигналов, для чего нажимаем кнопку Zoom to Full View.

Итак, судя по осциллограммам, мы можем видеть, что наш элемент защиты от дребезга работает идеально. Как только появляется фронт входного воздействия на порте INSIG, на выходе OUTSIG возникает импульс с периодом 256 мс. Величина эта постоянная и никакие последующие флуктуации на входе INSIG не в состоянии её изменить.

Так же мы можем наблюдать, как изменяются состояния внутренних сигналов и шин элемента защиты от дребезга.

Таким образом, в этом видеоуроке мы научились основам работы со встроенным HDL-симулятором ISim пакета программ XILINX ISE WebPack 13.2.

Загрузка конфигурации в Spartan™-3 Demo Board

[править]В этом видеоуроке рассматриваем, как назначить конкретные выводы кристалла ПЛИС нашему проекту, так же разбираем генерацию файла прошивки. И напоследок учимся непосредственно программировать ПЛИС.

ЦИФРОВАЯ СХЕМОТЕХНИКА В СИСТЕМАХ НА КРИСТАЛЛЕ

[править]РЕКОМЕНДУЕМАЯ ЛИТЕРАТУРА

[править]- Зотов, В.Ю. Проектирование цифровых устройств на основе ПЛИС фирмы Xilinx в САПР WebPACK ISE / В.Ю. Зотов. -- М.: Горячая линия-Телеком, 2003. -- 624 с.

- Кузелин, М.О. Современные семейства ПЛИС фирмы Xilinx: справочное пособие / М.О. Кузелин, Д.А. Кнышев, В.Ю. Зотов. -- М.: Горячая линия-Телеком, 2004. -- 440 с.

- Тарасов, И. Е. Разработка цифровых устройств на основе ПЛИС Xilinx с применением языка VHDL / И.Е. Тарасов. -- М.: Горячая линия-Телеком, 2005. -- 252 с.

- Зотов, В.Ю. Проектирование встраиваемых микропроцессорных систем на основе ПЛИС фирмы Xilinx в САПР WebPACK ISE / В.Ю. Зотов. -- М.: Горячая линия-Телеком, 2006. -- 520 с.

- Spartan-3 FPGA Family: Complete Data Sheet [Электронный ресурс] / Xilinx Inc., 2005 -- Режим доступа: http://direct.xilinx.com/bvdocs/publications/ds099.pdf(англ.). -- Яз. англ.

- Spartan-3 Starter Kit Board User Guide [Электронный ресурс] / Xilinx Inc., 2005 -- Режим доступа: http://direct.xilinx.com/bvdocs/userguides/ug130.pdf(англ.). -- Яз. англ.

- Spartan-3E FPGA Family: Complete Data Sheet [Электронный ресурс] / Xilinx Inc., 2006 -- Режим доступа: http://direct.xilinx.com/bvdocs/publications/ds312.pdf(англ.). -- Яз. англ.

- Spartan-3E Starter Kit User Guide [Электронный ресурс] / Xilinx Inc., 2006 -- Режим доступа: http://direct.xilinx.com/bvdocs/userguides/ug230.pdf(англ.). -- Яз. англ.

- Грушвицкий, Р.И. Проектирование систем на микросхемах программируемой логики / Р.И. Грушвицкий, А.Х. Мурсаев, Е.П. Угрюмов. -- СПб.: БХВ-Петербург, 2002. -- 608 с.

- Суворова, Е.А. Проектирование цифровых систем на VHDL / Е.А. Суворова, Ю.Е. Шейнин. -- СПб.: БХВ-Петербург, 2003. -- 576 с.

- Сергиенко, А.М. VHDL для проектирования вычислительных устройств / А.М. Сергиенко -- К.: ЧП "Корнейчук", ООО "ТИД ДС", 2003. -- 208 с.

- Бибило, П.Н. Основы языка VHDL / П.Н. Бибило. -- М.: СОЛОН-Р, 2002. -- 224 с.

- Бибило, П.Н. Системы моделирования интегральных схем на основе языка VHDL. StateCAD, ModelSim, LeonardoSpectrum / П.Н. Бибило. -- М.: СОЛОН Пресс, 2005. -- 384 с.

- Поляков, А.К. Языки VHDL и VERILOG в проектировании цифровой аппаратуры / А.К. Поляков. -- М.: СОЛОН-Пресс, 2003. -- 320 с.

- Максфилд K. Проектирование на ПЛИС. Курс молодого бойца -- Додэка XXI, 2007. -- 410 c.