SiLab С8051F34x datasheet

Документация к микропроцессорам семейства C8051F34x компании SiLab

[править]

Краткое описание

[править]C8051F340/1/2/3/4/5/6/7/8/9/A/B/C/D — интегральные однокристальные микроконтроллеры с USB интерфейсом.

-

Таблица 1.1. Руководство по выбору микроконтроллера

-

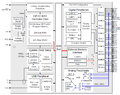

Рис. 1.1. Блок схема микроконтроллеров C8051F340/1/4/5

-

Рис. 1.2. Блок схема микроконтроллеров C8051F342/3/6/7

-

Рис. 1.3. Блок схема микроконтроллеров C8051F348/C

-

Рис. 1.4. Блок схема микроконтроллеров C8051F348/D

-

Рис. 1.5. Блок схема микроконтроллеров C8051F34A/B

Рабочие характеристики

[править]Внимание! превышение пределов указанных в таблице 2.1 может привести к выходу устройства из строя. В таблице приведены максимальные значения, работа устройства, при таких знаниях или выше допустимых рабочих значений, не допускается. Длительная работа при максимально допустимых параметрах может привести к нестабильной работе устройства.

| Параметр | Условия | Мин. | Норм. | Макс. | Единицы |

|---|---|---|---|---|---|

| Рабочая температура окружающей среды | –55 | 125 | °C | ||

| Температура хранения | –65 | 150 | °C | ||

| Напряжение на любом контакте ввода/вывода или на контакте RST, относительно земли GND | –0,3 | 5,8 | В | ||

| Напряжение на VDD относительно земли GND | –0,3 | 4,2 | В | ||

| Максимальный суммарный ток через VDD и GND | 500 | мА | |||

| Максимальный выходной ток утечки на любом контакте ввода/вывода или на контакте RST | 100 | мА |

Электрически характеристики

[править]От –40 до +85 °C, при частоте системной шины 25 МГц, если не явно не указаны другие условия.

Сноски:

- Для работы USB требуется напряжение питания не менее 3 В

- Для осуществления отладки частота системной шины (SYSCLK) должна быть не менее 32 кГц

- Теоретические характеристики. Эмпирических данных нет.

- Активный и пассивный IDD, для других значений напряжения и частоты, могут быть рассчитаны с помощью коэффициента чувствительности IDD (IDD Supply Sensitivity). Например, если VDD — 3 В, а не 3,3 В при частоте 24 МГц: IDD = 13.9 мА. Тогда, IDD = 13.9 мА + 0.46 • (3.0 В – 3.3 В) = 13.76 мА при 3 В и SYSCLK = 24 MHz.

- Для частот меньше 30 МГц IDD можно определить путем умножения целевой частоты на коэффициент чувствительность к частоте для данного диапазона. При таком подходе, определяется разность значения тока при 24 МГц (48 МГц) минус разница тока определенного коэффициентом чувствительности. Например: VDD = 3.3 В; SYSCLK = 35 МГц, IDD = 13.9 мА – (24 МГц – 35 МГц) • 0.44 мА/МГц = 18.74 мА.

- IDD без нагрузки (idle IDD), для частот менее 1 МГц, можно определить путем умножения целевой частоты на коэффициент чувствительность к частоте для данного диапазона. При таком подходе, определяется ток при 24 МГц (48 МГц) минус разница тока определенного коэффициентом чувствительности. Например: VDD = 3.3 В; SYSCLK = 5 МГц, Idle IDD = 8.25 мА – (24 МГц – 5 МГц) • 0.32 мА/МГц = 2.17 мА.

Остальные электрические характеристики приведены в разделах описывающих периферийные блоки.Шаблон:Wiki:Todo

Выводы микросхемы

[править]| Обозначение | Номер | Тип | Описание | |

|---|---|---|---|---|

| VDD | 10 | 6 | Питание вход/выход | Вход источника питания 2.7–3.6 В. Выход 3.3 В стабилизатора напряжения. См. раздел 8. |

| GND | 7 | 3 | Земля | |

| RST/ C2CK |

13 | 9 | D I/O | Сброс устройства (Reset). Отладочный вывод внутреннего POR или VDD с открытым стоком. Системная перезагрузка может быть вызвана внешними устройствами путем установки низкого потенциала (driving low) на срок не менее чем 15 мс. См. раздел 11. Тактовый сигнал для отладочного интерфейса C2. |

| C2D | 14 | — | D I/O | Двунаправленный сигнал данных отладочного интерфейса C2 |

| P3.0/ C2D |

— | 10 | D I/O | Порт 3.0. Данный порт описывается в разделе 15 Двунаправленный сигнал данных отладочного интерфейса C2 |

| REGIN | 11 | 7 | Power In | Вход встроенного стабилизатора напряжения — 5 В. |

| VBUS | 12 | 8 | D In | Вход VBUS, должен быть подключен к сигнальной линии VBUS сети USB. Напряжение 5 В на этом контакте свидетельствует о подключении сети USB. |

| D+ | 8 | 4 | D I/O | USB D+. |

| D- | 9 | 5 | D I/O | USB D–. |

| P0.0-7 | (6, 5, 4, 3, 2, 1 , 48, 47) | (2, 1, 32, 31, 30, 28, 28, 27) | D I/O or A In | Порты. См. раздел 15 |

| P1.0-7 | (46, 45, 44, 43, 42, 41, 40, 39) | (26, 25, 24, 23, 22, 21, 20, 19) | D I/O или A In | Порты. См. раздел 15 |

| P2.0-7 | (38, 37, 36, 35, 34, 33, 32, 31) | (18, 17, 16, 15, 14, 13, 12, 11) | D I/O или A In | Порты. См. раздел 15 |

| P3.0-7 | (30, 29, 28, 27, 26, 25, 24, 23) | — | D I/O или A In | Порты. См. раздел 15 |

| P4.0-7 | (22, 21, 20, 19, 18, 17, 16, 15) | — | D I/O или A In | Порты. См. раздел 15 |

-

схема выводов

-

Нумерация выводов C8051F342/3/6/7/9/A/B/D-GQ

-

Нумерация выводов C8051F340/1/4/5/8/C-GQ

АЦП

[править]

АЦП -- аналогово-цифровой преобразователь (англ. Analog-digital convertor, ADC)

Подсистема ADC0 состоит из двух мультиплексоров (адресуемых через AMUX0) и 10-и битного усредняющего регистра ADC с интегрированным следяще-запоминающим и программируемым детектором (англ. window detector).

AMUX0, режимы преобразования и детектор (англ. window detector) все конфигурируются программно через регистры специального назначения (англ. Special Function Registers, SFR) см. рис 5.1

ADC0 работает как в одноканальном так и в дифференциальном режиме, и может быть сконфигурирован для измерения напряжения на контактах входного интерфейса (англ. port pins), выходного сигнала температурного датчика или напряжения питания VDD, VREF, GND.

Параметры AMUX0 детально описаны в разделах "SFR Definition 5.1" и "SFR Definition 5.2". Подсистема ADC0 задействована только если установлен бит (в значение 1) AD0EN в контрольном регистре ADC0 (ADC0CN). Иначе подсистема находится в энергосберегающем выключенном режиме.

Аналоговый мультиплексор

[править]AMUX0 соединяется с ADC посредством положительного и отрицательного входа. Положительный вход (AIN+) может быть соединен с температурным сенсором или положительным источником питания (VDD). Отрицательный вход (AIN-) может быть подсоединен к VREF, или GND. Когда земля GND используется как отрицательный вход, ADC0 работает в одноканальном режиме; во всех других случаях, ADC0 работает в дифференциальном режиме. Входным каналам соответствуют соответствующие регистры AMX0P и AMX0N, описанные в определениях SFR (регистры специального назначения, англ. Special Function Registers) (разделы 5.1 и 5.2)

Формат кодов преобразований отличается в одноканальном и дифференциальном режимах. Регистры ADC0H и ADC0L получают старший и младший байты кода выходного преобразования ADC по окончании каждого преобразования. Данные могут быть выровнены по правому или левому краю, в зависимости от значения бита выравнивания AD0LJST (ADC0CN.0). В одноканальном режиме, коды преобразования представлены как десятибитные беззнаковые целые (10-bit unsigned integer). Входные данные представляются в виде соответствующего значения от "0" до VREF x 1023/1024. Ниже приведены примеры как для правого так и для левого выравнивания. Неиспользуемые биты в регистрах ADC0H и ADC0L отмечены нулями.

В дифференциальном режиме коды режимов преобразования представлены в виде второго двоичного дополнения десятибитовых знаковых чисел. Входные значения представляются соответствующим числом в диапазоне –VREF ... VREF x 511/512. Ниже приведены примеры как для правого так и для левого выравнивания. Для правого выпавнивания, неиспользуемые старшие разряды (most significant bit, MSB) регистра ADC0H используются как расширение знака (sign-extension) двоичного слова. Для левого выравнивания, неиспользуемые младшие значащие биты регистра ADC0L заполняются нулями.

Важное замечание о конфигурации входа ADC0: Контакты (pins), выбранные в качестве входных для ADC0, должны быть сконфигурированы как аналоговые входы и не должны быть задействованы в цифровом коммутаторе (Digital Crossbar). Для того чтобы сконфигурировать контакт как аналоговый, необходимо установить в ноль соответствующий бит регистра PnMDIN. Для принудительного исключения контакта из массива цифрового коммутатора, необходимо установить в "1" соответствующий бит регистра PnSKIP. Более детальную информацию вы можете найти в разделе "15. Порты ввода/вывода".

Температурный сенсор

[править]Передаточная функция температурного сенсора показана на изображении 5.2. Напряжение на выходе (VTEMP) -- это положительный вход ADC когда температурный сенсор выбран битами AMX0P4-0 регистра AMX0P. Значения смещения (Offset) и отклонения (Slope) приведены в таблице 5.1.

Показания откалиброванного температурного датчика линейны и подходят для измерения относительного изменения температуры. Для абсолютного измерения температуры рекомендуется калибровка смещения (offset) и/или приращения (gain). Чаще всего простая калибровка состоит из следующих этапов:

- Начать наблюдение изменения температуры окружающей среды

- Включить устройство и дать ему нагреется

- Произвести АЦП преобразование с температурным датчиком в качество положительного входа и "землей" (GND) в качестве отрицательного входа.

- Измерить смещение и сохранить в энергонезависимой памяти для возможности последующего анализа серии измерений.

Изображение 5.3 демонстрирует типичную ошибку простой калибровки при 25°C. Необходимо учитывать, что параметры влияющие на АЦП преобразование, в частности опорное напряжение, могут также влиять на измеряемое значение температуры.

Режимы работы

[править]Максимальная частота дискретизации АЦП0 составляет 200 ksps. Частота дискретизации определяется как процент от частоты тактового (системного) генератора, определяется битами AD0SC регистра ADC0CF (системная частота / [AD0SC + 1] при 0 <= AD0SC <= 31).

Инициализация преобразования

[править]В зависимости от программируемых состояний битов инициализации АЦП — AD0CM2–0 (англ. Start of Conversion Mode bits) регистра ADC0CN, преобразование может быть инициализировано одним из пяти способов:

- Записью двоичной единицы в AD0BUSY бит регистра ADC0CN

- Переполнением таймера 0 (например при непрерывном преобразовании реального времени)

- Переполнением таймера 2

- Переполнением таймера 1

- При возрастании фронта входного импульса CNVSTR

- Переполнением таймера 3

Запись двоичной единицы в AD0BUSY вызывает программный запуск АЦП0, таким образом преобразование начинается "по требованию". Бит AD0BUSY содержит единицу во время всего процесса преобразования и сбрасывается в ноль после его завершения. Сброс AD0BUSY вызывает прерывание (если прерывания разрешены) и устанавливает флаг прерывания (AD0INT) АЦП0. Заметьте, что для запроса завершения АЦП преобразования, необходимо использовать флаг прерывания ADC0 — AD0INT. Данные преобразования доступны в регистрах данных АЦП0 (ADC0) — ADC0H:ADC0L, когда бит AD0INT равен логической единице. Также важно понимать, что когда начало преобразования вызвано переполнением таймера 2 или 3, то используется переполнение младшего байта (англ. Low Byte) в восьмибитном режиме работы таймера; старший байт используется в шестнадцатибитном режиме работы таймера. Конфигурирование таймеров подробно описана в разделе "21 Таймеры".

Важное замечание по использованию CNVSTR: входной контакт CNVSTR также является контактом интерфейсного разъема (Port pin). Когда CNVSTR используется как источник преобразования для АЦП0, для него необходимо отключить функцию контактом интерфейсного разъема, чтобы он игнорировался цифровым коммутатором (Digital Crossbar). Для этого необходимо установить в единицу соответствующий бит PnSKIP цифрового коммутатора. Более детальная информация приведена в разделе "15. Порты ввода/вывода".

Режим слежения

[править]Бит AD0TM регистра ADC0CN контролирует следяще-запоминающий режим АЦП0 (ADC0). По умолчанию АЦП0 постоянно доступен для слежения (наблюдения), за исключением времени когда идет преобразование. При не нулевом значении бита AD0TM, АЦП0 находится в энергосберегающем следяще-запоминающем режиме. В этом режиме каждое преобразование упреждается трехтактовым (3 SAR) трекинг-периодом (tracking period) (после сигнала "начало преобразования"). Когда для инициализации преобразования в энергосберегающем режиме слежения используется CNVSTR сигнал, то АЦП0 осуществляет слежение (наблюдение) только при низком потенциале CNVSTR; преобразование начинается при возрастании фронта входного импульса CNVSTR (рис. 5.4). Режим слежение отключается когда устройство переходит в энергосберегающий режим ожидания (standby) или режим сна (англ. sleep). Энергоэффективный следяще-запоминающий режим используется когда часто меняются установки AMUX, в связи с требуемым временем на установление сигнала (см. в разделе "5.3.3 Необходимое время для установления сигнала").

Необходимое время для установления сигнала

[править]Когда меняется конфигурация для входа АЦП0 (например выбирается другой AMUX0), необходимо некоторое минимальное время наблюдения для получения точного (правильного) преобразования. Это время наблюдения определяется сопротивлением AMUX0, емкостью дискретизации (sampling capacitance) АЦП0, сопротивлением на внешнем входе (external source resistance), что требуется учитывать для точности преобразований. Заметьте, что в энергоэффективном режиме наблюдения (слежения, англ. tracking) используются три такта (3 SAR clocks) для наблюдения в начале каждого преобразования. В большинстве случаев три такта достаточно для установления сигнала.

На изображении 5.5 показаны эквивалентные электрические схемы входных каскадов для одноканального и дифференциального режимов. Заметьте, что эквивалентное время для обоих схем одинаково. Время установления сигнала АЦП0 для получения заданной установочной точности (settling accuracy, SA) может быть приближенно вычислено с помощью выражения 5.1 Когда производятся измерения с помощью температурного датчика или VDD по отношению к "земле" GND, RTOTAL сводиться к RMUX.

Где:

- SA — установочная точность, представленная как частное от LSB (например, коэффициент установки 0.25 — 1/4 от LSB)

- t — необходимое время для установления сигнала в секундах

- RTOTAL — сумма сопротивления AMUX0 и любого внешнего сопротивления

- n — разрешение АЦП в битах (т.е. 10)

Программируемый детектор диапазона значений

[править]Программируемый детектор диапазона значений АЦП постоянно сравнивает результат преобразования АЦП0 с программно заданными границами, и уведомляет систему когда выполняется определенное условие. Это особенно эффективно в системах управляемых прерываниями, помогает уменьшить объем программного кода, снижает нагрузку на ЦП за счет более быстрого отклика. Флаг прерывания детектора диапазона значений (AD0WINT регистра ADC0CN) может также использоваться в режиме опроса. Регистры "больше чем" (ADC0GTH, ADC0GTL) и "меньше чем" (ADC0LTH, ADC0LTL) хранят сравниваемые значения. Флаг детектора диапазона значений может быть программно использован для определения находится ли измеряемое значение в определенных границах, за счет использования регистров АЦП0 "больше чем" и "меньше чем".

При программировании детектора диапазона значений необходимо использовать тот же формат как и в конфигурации текущего АЦП: правое или левое выравнивание, знаковое или без знаковое значение (для одноканального или дифференциального режимов соответственно).

Детектор диапазона значений в одноканальном режиме

[править]На изображении 5.6 показан пример сравнения диапазонов для правого выравнивания, одноканального режима, с ADC0LTH:ADC0LTL = 0x0080 (128d) и ADC0GTH:ADC0GTL = 0x0040 (64d). В одноканальном режиме входной вольтаж может принимать значения от нуля до x (1023/1024) по отношению к "земле" GND, и представляется десятибитным без знаковым целым значением. В левом примере прерывание AD0WINT будет сгенерировано если двоичное слово преобразования АЦП0 (ADC0H:ADC0L) находится в диапазоне определенном в ADC0GTH:ADC0GTL и в ADC0LTH:ADC0LTL (если 0x0040 < ADC0H:ADC0L < 0x0080). В примере справа прерывание AD0WINT будет сгенерировано если двоичное слово преобразования АЦП0 находится вне диапазона определенного регистрами ADC0GT и ADC0LT (если ADC0H:ADC0L < 0x0040 или ADC0H:ADC0L > 0x0080) Изображение 5.7 демонстрирует пример с использованием левого выравнивания с одинаковыми конфигурациями регистров ADC0GT и ADC0LT.

-

Одноканальный режим, правое выравнивание

-

Одноканальный режим, левое выравнивание

Детектор диапазона значений в дифференциальном режиме

[править]На изображении 5.8 показан пример сравнения диапазонов для правого выравнивания, дифференциального режима, с ADC0LTH:ADC0LTL = 0x0040 (+64d) и ADC0GTH:ADC0GTH = 0xFFFF (-1d). В дифференциальном режиме измеряемый вольтаж между входными контактами может принимать значения в диапазоне -VREF and VREF * (511/512). Выходные значения представляются в виде десятибитового 2-го двоичного дополнения знаковых целых значений. В примере слева прерывание AD0WINT будет сгенерированно если двоичное слово преобразования АЦП0 (ADC0H:ADC0L) находится в диапазоне определенном в ADC0GTH:ADC0GTL и ADC0LTH:ADC0LTL (если 0xFFFF (-1d) < ADC0H:ADC0L < 0x0040 (64d)). В примере справа прерывание AD0WINT будет сгенерированно если двоичное слово преобразования АЦП0 (ADC0H:ADC0L) находится вне диапазона определенного в регистрах ADC0GT и ADC0LT (если ADC0H:ADC0L < 0xFFFF (-1d) или ADC0H:ADC0L > 0x0040 (+64d)). На изображении 5.9 приведен пример с использованием левого выравнивания с одинаковыми конфигурациями регистров ADC0GT и ADC0LT.

-

Дифференциальный режим, правое выравнивание

-

Дифференциальный режим, левое выравнивание

Опорное напряжение

[править]| Этот раздел статьи ещё не написан. Согласно замыслу одного или нескольких участников Викиучебника, на этом месте должен располагаться специальный раздел.

Вы можете помочь проекту, написав этот раздел. |

Компараторы

[править]| Этот раздел статьи ещё не написан. Согласно замыслу одного или нескольких участников Викиучебника, на этом месте должен располагаться специальный раздел.

Вы можете помочь проекту, написав этот раздел. |

Стабилизатор напряжения

[править]| Этот раздел статьи ещё не написан. Согласно замыслу одного или нескольких участников Викиучебника, на этом месте должен располагаться специальный раздел.

Вы можете помочь проекту, написав этот раздел. |

Ядро CIP-51

[править]Ядро микропроцессорного устройства управления (microprocessor control unit, MCU) представляет собой микроконтроллер архитектуры CIP-51. Стандарт CIP-51 полностью совместим с набором инструкций MCS-51™; допускается использование стандартных 803x/805x ассемблеров и компиляторов для разработки программного обеспечения. Данное семейство микроконтроллеров включает расширенный набор всех периферийных элементов предусмотренных стандартом 8051. Включая четыре шестнадцатибитных счетчика/таймера, улучшенный полнодуплексный универсальный асинхронный приёмопередатчик, УАПП (Universal Asynchronous Receiver/Transmitter, UART), улучшенный последовательный синхронный периферийный интерфейс (serial peripheral interface, SPI), 256 байт внутренней оперативной памяти, 128 байт адресного пространства специальных регистров (Special Function Register, SFR), 25 портов ввода/вывода. CIP-51 также включает встроенное отладочное устройство, и прямые интерфейсы аналоговых и цифровых подсистем для обеспечения возможности сбора информации или контролирования состояния системы на базе одно устройства.

Ядро микроконтроллера CIP-51 наследует как организацию и периферию стандарта 8051 так и свою дополнительную периферию и функциональность расширяющую применяемость устройства (см. Рис. 9.1). Архитектура CIP-51 включает следующие особенности:

|

|

Среда выполнения. В CIP-51 используется конвейерная архитектура обработки команд, что значительно увеличивает пропускную способность по сравнению с архитектурой 8051. В стандарте 8051 все инструкции, исключая MUL и DIV, выполняются в течении 12 или 24 тактов, при обычной максимальной частоте 12 Мгц. А ядро CIP-51 выполняет 70% инструкций за один или два такта, и не одна инструкция не выполняется дольше восьми тактов.

С учетом тактовой частоты CIP-51 равной 25 Мгц, пиковая пропускная способность равняется двадцати пяти миллионам команд в секунду (Million Instructions Per Second, MIPS). Общее количество инструкций равняется 109-и.

Программирование и отладка. Запись программы во внутреннюю Flash память и обмен отладочной информацией реализуется с помощью двухканального интерфейса C2 (Silicon Labs Development Interface). Flash память также доступна для побайтового чтения/записи из внутренней программы с помощью команд MOVC и MOVX. Это позволяет сохранять некоторые данные в энергонезависимой памяти и позволяет программа динамически изменять свой код при необходимости.

Интерфейс разработки C2 позволяет интуитивно (используя внутренние ресурсы), быстро (full speed), производить внутреннюю отладку средствами микроконтроллера, установленного в готовом устройстве. Логика отладки поддерживает контроль и изменение регистров памяти, установку точек останова (breakpoints), пошаговое выполнение, и инициированное прекращение работы программы. Все аналоговые и цифровые подсистемы полноценно работают во время отладки через интерфейс C2. Два контакта интерфейса C2 могут быть использованы пользовательскими функциями, позволяя проводить внутреннюю отладку не занимая дополнительные выводы (контакты). Подробнее интерфейс C2 описан в разделе "23. Интерфейс C2".

CIP-51 поддерхивается инструментами разработчика от компании Silicon Labs и других компаний. Silicon Labs предоставляет интегрированную среду разработки (integrated development environment, IDE), включающую редактор, отладчик, инструментарий для работы с программатором. Также в набор разработчика входит компоновщик связей (linker), "С" компилятор, 8051 ассемблер. Доступно большое количество сторонних компиляторов, которые можно непосредственно использовать в среде разработки.

Набор инструкций

[править]Набор инструкции CIP-51 контроллера полностью совместим с стандартом инструкций MCS-51™. Инструменты разработчика которые поддерживают 8051 могут быть использованы для разработки программного обеспечения для CIP-51. Инструкции CIP-51 являются бинарными эквивалентами аналогичных инструкций MCS-51™, включая машинные коды операций, режимы адресации и механизмы взаимодействия с регистрами-флагами состояния процессора. Тем не менее, затрачиваемое машинное время (instruction timing) отличается от описанного в стандарте 8051.

Инструкции и процессорное время

[править]Во многих реализациях 8051, делается различие между тактами и машинными циклами, машинные циклы занимают примерно от двух до 12 тактов. Однако, реализация CIP-51 оперирует исключительно временем выраженном в тактах. Время выполнения всех инструкций приведено в размерности тактов.

В связи с конвейерной архитектурой CIP-51, большинство инструкций выполняется за тактовое время равное количеству байт в инструкции. Инструкции условного ветвления выполняются на пару тактов быстрее когда условие выполнения ветвления не выполняется, по сравнению с временем когда условие ветвления выполняется.

Инструкция MOVX и память программы

[править]Инструкция MOVX в CIP-51 имеет три назначения: реализует доступ к встроенной памяти XRAM, доступ к встроенной программной Flash памяти, и доступ к внешней памяти (только в C8051F340/1/4/5/8). Доступ к встроенной программной Flash памяти позволяет пользовательскому программному обеспечению динамически изменять программный код и использовать пространство программной памяти для долгосрочного хранения данных (энергонезависимое хранилище) (см. раздел "12. Flash память"). Взаимодействие с внешней памятью подробно описано в разделе "13 XRAM и внешняя память".

Организация памяти

[править]Организация памяти в системном контроллере CIP-51 аналогично реализации стандарта 8051. Существуют две отдельных области памяти: память программы и память данных. Программная память и паять данных разделяют одно и тоже адресное пространство, но доступ к ним осуществляется с помощью различных типов инструкций. Организация памяти CIP-51 показана на изображении 9.3

Память программы

[править]Размер памяти ядра CIP-51 составляет 64 Кб. Семейства микроконтроллеров C8051F34x могут поставляться с 64 или 32-я килобайтами программной памяти в виде встроенной перепрограммируемой Flash памяти. Помните, что в версиях микроконтроллеров C8051F34x с 64 Кб памяти, адреса выше 0xFBFF зарезервированы.

Изначально предполагается, что память программы доступна только для чтения. Однако, CIP-51 позволяет производить запись в программную область памяти установив бит "Program Store Write Enable" (PSCTL.0) и используя инструкцию MOVX. Это позволяет пользовательскому программному обеспечению динамически изменять программный код и использовать пространство программной памяти для долгосрочного хранения данных (энергонезависимое хранилище) (см. раздел "12. Flash память")

Память данных

[править]CIP-51 включает 256 байт памяти отведенной под данные в диапазоне от 0x00 до 0xFF. Младшие 128 байт используются для регистров общего назначения и в качестве сверхоперативной памяти. Для доступа к младшим байтам можно использовать как прямую так и не прямую адресацию. Область 0x00 ... 0x1F адресуется как четыре банка регистров общего назначения, каждый банк состоит из восьми байтовых регистров. Следующие 16 байт — 0x20 ... 0x2F, могут быть адресованы побайтово или как 128 битное хранилище доступное с помощью прямой адресации.

Старшие 128 байт памяти данных доступны только через непрямой метод адресации. Эта область памяти имеет тот же диапазон, что и регистры специального назначения (Special Function Registers, SFR) но физически эти области разделены друг от друга. При адресации выше above режим адресации использованный инструкцией определяет производится ли доступ к области данных или к регистрам SFR. Инструкции которые используют прямую адресацию получают доступ к SFR. Инструкции которые используют не прямую адресацию получают доступ к старшим 128 байтам памяти данных.

Регистры общего назначения

[править]Младшие 32 байта памяти данных — 0x00 ... 0x1F адресуются как четыре банка регистров общего назначения. Каждый банк состоит из восьми байтовых регистров обозначаемых как R0 ... R7. Доступ к банкам производится по одному. Два бита в двоичном слове статуса программы, RS0 (PSW.3) и RS1 (PSW.4), определяют какой банк является доступным в данный момент (см. описание PSW в определениях SFR раздел 9.4). Это обеспечивает возможность быстрого контекстного переключения при входе в подпрограммы и позволяет прерывать служебные программы. Непрямые методы адресации используют регистры R0 и R1 как индексные.

Битовое адресное пространство

[править]В дополнение к памяти данных с прямым доступом адресуемой побайтово, также доступно 128 единичных бит в виде 16 хранилищ с адресами от 0x20 до 0x2F, адресуемых побитово. Каждый бит имеет адрес от 0x00 до 0x7F. Нулевой бит с байтовым адресом 0x20 имеет битовый адрес 0x00, тогда как седьмой бит с таким же байтовым адресом будет иметь битовый адрес — 0x07. Седьмой бит с адресом 0x2F будет иметь битовый адрес 0x7F. Битовый доступ отличается от байтового типом используемой инструкции (битовые операнды источника и приемника расположены противоположно положению байтовых операндов).

Язык ассемблера MCS-51™ допускает альтернативный синтаксис в формате XX.B для побитовой адресации, где XX это байтовый адрес, а B — позиция бита относительно байта. К примеру, инструкция:

MOV C, 22h.3

переместит логическое значение по адресу 0x13 (третий бит байта с адресом 0x22) в флаг переноса.

Стек

[править]Стек программы может располагаться в произвольном месте 256-и байтного пространства памяти данных. Положение стека запоминается с помощью указателя (SP, 0x81) SFR. SP хранит указатель на последнее записанное значение. Следующее значение смещается на SP+1 и SP инкриминируется. Сброс стека записывает в SP инициализирующее значение — 0x07. Тогда , первое записанное значение в стек помещается по адресу 0x08, который также соответствует первому регистру (R1) первого банка регистров. Таким образом, когда используется больше одного банка регистров, SP нужно размещать в области памяти данных, которая не используется. Размер стека может доходить до 256 байт.

Регистры специального назначения

[править]Область памяти от 0x80 до 0xFF с прямым доступом содержит регистры специального назначения (special function registers, SFR). Регистры специального назначения обеспечивают контроль и обмен данными с ресурсами и периферией CIP-51. Кроме специальных регистров описанных стандартом 8051, CIP-51 содержит дополнительные регистры SFR используемые для взаимодействия с подсистемами характерных для данного типа микроконтроллеров и их конфигурирования. Это обеспечивает дополнительную функциональность при сохранении совместимости с набором инструкций MCS-51™. Таблица 9.2 содержит список специальных регистров используемых в контроллерах CIP-51.

Доступ к SFR производится в любое время с помощью прямой адресации с 0x80 по 0xFF. Регистры SFR которые заканчиваются в 0x0 или 0x8 (например P0, TCON, SCON0, IE и т. д.) адресуются как биты. Все другие регистры адресуются только как байты. Неиспользуемое адресное пространство в области SFR зарезервировано для расширения функциональности в будущем. Обращение к этим областям дает непредсказуемый результат. В таблице 9.3 приведено описание всех регистров SFR.

См. также: полный список регистров, адресов и переменных

| Значение | Имя переменной | Описание | Примечания | ||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 0xE0 | ACC | Аккумулятор | C8051F340.h | ||||||||||||||||||||

| 0xBC | ADC0CF | Конфигурация ADC0 (АЦП 0) | C8051F340.h | ||||||||||||||||||||

| 0xE8 | ADC0CN | Управление АЦП0 ADC0 | C8051F340.h | ||||||||||||||||||||

| 0xC4 | ADC0GTH | верхний регистр сравнения "больше" ADC0 (АЦП 0) | C8051F340.h | ||||||||||||||||||||

| 0xC3 | ADC0GTL | нижний регистр сравнения "больше" ADC0 (АЦП 0) | C8051F340.h | ||||||||||||||||||||

| 0xBE | ADC0H | Верхний регистр ADC0 (АЦП 0) | C8051F340.h | ||||||||||||||||||||

| 0xBD | ADC0L | Нижний регистр ADC0 (АЦП 0) | C8051F340.h | ||||||||||||||||||||

| 0xC6 | ADC0LTH | верхний регистр сравнения "меньше" ADC0 (АЦП 0) | C8051F340.h | ||||||||||||||||||||

| 0xC5 | ADC0LTL | нижний регистр сравнения "меньше" ADC0 (АЦП 0) | C8051F340.h | ||||||||||||||||||||

| 0xBA | AMX0N | Выбор отрицательного канала AMUX0 | C8051F340.h | ||||||||||||||||||||

| 0xBB | AMX0P | Выбор положительного канала AMUX0 | C8051F340.h | ||||||||||||||||||||

| 0xF0 | B | Регистр B выполняет роль второго регистра-аккумулятора. См. также описание регистра ACC | C8051F340.h | ||||||||||||||||||||

| 0x8E | CKCON | Управление частотой (англ. Clock Control) | C8051F340.h | ||||||||||||||||||||

| 0xB9 | CLKMUL | Умножитель частоты | C8051F340.h | ||||||||||||||||||||

| 0xA9 | CLKSEL | Выбор частоты | C8051F340.h | ||||||||||||||||||||

| 0x9B | CPT0CN | Управление компаратором номер 0 | C8051F340.h | ||||||||||||||||||||

| 0x9D | CPT0MD | Выбор режима работы компаратора 0 | C8051F340.h | ||||||||||||||||||||

| 0x9F | CPT0MX | Выбор MUX-а компаратора 0 | C8051F340.h | ||||||||||||||||||||

| 0x9A | CPT1CN | Управление компаратором номер 1 | C8051F340.h | ||||||||||||||||||||

| 0x9C | CPT1MD | Выбор режима работы компаратора 1 | C8051F340.h | ||||||||||||||||||||

| 0x9E | CPT1MX | Выбор MUX-а компаратора 1 | C8051F340.h | ||||||||||||||||||||

| 0x83 | DPH |

Старший байт указателя данных. Регистр DPL представляет собой старший байт 16-ти битного регистра DPTR. DPTR используется для непрямого доступа к памяти. См. также регистр DPL. |

C8051F340.h | ||||||||||||||||||||

| 0x82 | DPL |

Младший байт указателя данных. Регистр DPL представляет собой младший байт 16-ти битного регистра DPTR. DPTR используется для непрямого доступа к памяти. См. также регистр DPH. |

C8051F340.h | ||||||||||||||||||||

| 0xE6 | EIE1 | Задействовать первое расширенное прерывание | C8051F340.h | ||||||||||||||||||||

| 0xE7 | EIE2 | Задействовать второе расширенное прерывание | C8051F340.h | ||||||||||||||||||||

| 0xAA | EMI0CN | Управление интерфейсом внешней памяти | C8051F340.h | ||||||||||||||||||||

| 0x85 | EMI0CF | Конфигурирование EMIF | C8051F340.h | ||||||||||||||||||||

| 0x84 | EMI0TC | Тайминг (счетчик времени) EMIF | C8051F340.h | ||||||||||||||||||||

| 0xB7 | FLKEY | Флеш "Lock and Key" | C8051F340.h | ||||||||||||||||||||

| 0xB6 | FLSCL | Масштабирование Flash | C8051F340.h | ||||||||||||||||||||

| 0xA8 | IE | Включение режима обработки прерываний | C8051F340.h | ||||||||||||||||||||

| 0xB8 | IP | Приоритете прерываний | C8051F340.h | ||||||||||||||||||||

| 0xE4 | IT01CF | Конфигурирование каналов INT0/INT1 | C8051F340.h | ||||||||||||||||||||

| 0xB3 | OSCICL | Калибровка внутреннего осциллятором (генератором частоты) | C8051F340.h | ||||||||||||||||||||

| 0xB2 | OSCICN | Управление внутренним осциллятором (генератором частоты) | C8051F340.h | ||||||||||||||||||||

| 0x86 | OSCLCN | Управление внутренним низкочастотным осциллятором (тактовым генератором) | C8051F340.h | ||||||||||||||||||||

| 0xB1 | OSCXCN | Управление внешним осциллятором (генератором частоты) | C8051F340.h | ||||||||||||||||||||

| 0x80 | P0 | Блокировка нулевого порта | C8051F340.h | ||||||||||||||||||||

| 0xF1 | P0MDIN | Конфигурирование режима ввода данных порта 0 | C8051F340.h | ||||||||||||||||||||

| 0xA4 | P0MDOUT | Конфигурация режима передачи (англ. Output Mode) порта 0 | C8051F340.h | ||||||||||||||||||||

| 0xD4 | P0SKIP | Пропуск нулевого порта | C8051F340.h | ||||||||||||||||||||

| 0x90 | P1 | Блокировка первого порта | C8051F340.h | ||||||||||||||||||||

| 0xF2 | P1MDIN | Конфигурирование режима ввода данных порта 1 | C8051F340.h | ||||||||||||||||||||

| 0xA5 | P1MDOUT | Конфигурация режима передачи (англ. Output Mode) порта 1 | C8051F340.h | ||||||||||||||||||||

| 0xD5 | P1SKIP | Пропуск первого порта | C8051F340.h | ||||||||||||||||||||

| 0xA0 | P2 | Блокировка второго порта | C8051F340.h | ||||||||||||||||||||

| 0xF3 | P2MDIN | Конфигурирование режима ввода данных порта 2 | C8051F340.h | ||||||||||||||||||||

| 0xA6 | P2MDOUT | Конфигурация режима передачи (англ. Output Mode) порта 2 | C8051F340.h | ||||||||||||||||||||

| 0xD6 | P2SKIP | Пропуск второго порта | C8051F340.h | ||||||||||||||||||||

| 0xB0 | P3 | Блокировка третьего порта | C8051F340.h | ||||||||||||||||||||

| 0xF4 | P3MDIN | Конфигурирование режима ввода данных порта 3 | C8051F340.h | ||||||||||||||||||||

| 0xA7 | P3MDOUT | Конфигурация режима передачи (англ. Output Mode) порта 3 | C8051F340.h | ||||||||||||||||||||

| 0xDF | P3SKIP | Пропуск третьего порта | C8051F340.h | ||||||||||||||||||||

| 0xC7 | P4 | Блокировка четвертого порта | C8051F340.h | ||||||||||||||||||||

| 0xF5 | P4MDIN | Конфигурирование режима ввода данных порта 4 | C8051F340.h | ||||||||||||||||||||

| 0xAE | P4MDOUT | Конфигурация режима передачи (англ. Output Mode) порта 4 | C8051F340.h | ||||||||||||||||||||

| 0xD8 | PCA0CN | Управление нулевым программируемым счетчиком-массивом, ПСМ0 (Programmable Counter Array, PCA0) | C8051F340.h | ||||||||||||||||||||

| 0xFC | PCA0CPH0 | ПСМ0 (Programmable Counter Array, PCA0) верхний регистр нулевой ловушки (англ. Capture) | C8051F340.h | ||||||||||||||||||||

| 0xEA | PCA0CPH1 | ПСМ0 (Programmable Counter Array, PCA0) верхний регистр первой ловушки (англ. Capture) | C8051F340.h | ||||||||||||||||||||

| 0xEC | PCA0CPH2 | ПСМ0 (Programmable Counter Array, PCA0) верхний регистр второй ловушки (англ. Capture) | C8051F340.h | ||||||||||||||||||||

| 0xEE | PCA0CPH3 | ПСМ0 (Programmable Counter Array, PCA0) верхний регистр третьей ловушки (англ. Capture) | C8051F340.h | ||||||||||||||||||||

| 0xFE | PCA0CPH4 | ПСМ0 (Programmable Counter Array, PCA0) верхний регистр четвертой ловушки (англ. Capture) | C8051F340.h | ||||||||||||||||||||

| 0xFB | PCA0CPL0 | ПСМ0 (Programmable Counter Array, PCA0) нижний регистр нулевой ловушки (англ. Capture) | C8051F340.h | ||||||||||||||||||||

| 0xE9 | PCA0CPL1 | ПСМ0 (Programmable Counter Array, PCA0) нижний регистр первой ловушки (англ. Capture) | C8051F340.h | ||||||||||||||||||||

| 0xEB | PCA0CPL2 | ПСМ0 (Programmable Counter Array, PCA0) нижний регистр второй ловушки (англ. Capture) | C8051F340.h | ||||||||||||||||||||

| 0xED | PCA0CPL3 | ПСМ0 (Programmable Counter Array, PCA0) нижний регистр третьей ловушки (англ. Capture) | C8051F340.h | ||||||||||||||||||||

| 0xFD | PCA0CPL4 | ПСМ0 (Programmable Counter Array, PCA0) нижний регистр четвертой ловушки (англ. Capture) | C8051F340.h | ||||||||||||||||||||

| 0xDA | PCA0CPM0 | Регистр режима 0-го модуля нулевого программируемого счетчика-массива, ПСМ0 (Programmable Counter Array, PCA0) | C8051F340.h | ||||||||||||||||||||

| 0xDB | PCA0CPM1 | Регистр режима 1-го модуля нулевого программируемого счетчика-массива, ПСМ0 (Programmable Counter Array, PCA0) | C8051F340.h | ||||||||||||||||||||

| 0xDC | PCA0CPM2 | Регистр режима 2-го модуля нулевого программируемого счетчика-массива, ПСМ0 (Programmable Counter Array, PCA0) | C8051F340.h | ||||||||||||||||||||

| 0xDD | PCA0CPM3 | Регистр режима 3-го модуля нулевого программируемого счетчика-массива, ПСМ0 (Programmable Counter Array, PCA0) | C8051F340.h | ||||||||||||||||||||

| 0xDE | PCA0CPM4 | Регистр режима 4-го модуля нулевого программируемого счетчика-массива, ПСМ0 (Programmable Counter Array, PCA0) | C8051F340.h | ||||||||||||||||||||

| 0xFA | PCA0H | Верхний регистр счетчика ПСМ0 (Programmable Counter Array, PCA0) | C8051F340.h | ||||||||||||||||||||

| 0xF9 | PCA0L | Нижний регистр счетчика ПСМ0 (Programmable Counter Array, PCA0) | C8051F340.h | ||||||||||||||||||||

| 0xD9 | PCA0MD | Установка режима нулевого программируемого счетчика-массива, ПСМ0 (Programmable Counter Array, PCA0) | C8051F340.h | ||||||||||||||||||||

| 0x87 | PCON | Управление питанием | C8051F340.h | ||||||||||||||||||||

| 0xAF | PFE0CN | Управление механизмом предварительной выборки | C8051F340.h | ||||||||||||||||||||

| 0x8F | PSCTL | Управление чтением/записью хранилища программы | C8051F340.h | ||||||||||||||||||||

| 0xD0 | PSW | Строка состояния программы (англ. Program Status Word, PSW)

0. Флаг четности. Этот бит устанавливается в единицу. если сумма восьми бит в аккумуляторе не четная и сбрасывается если сумма бит четная. 1. F1: Пользовательский флаг 1. Это адресуемый бит общего назначения который используется программой микроконтроллера. 2. OV: Флаг переполнения. Этот тит устанавливается в единицу если:

Во всех других случаях бит OV сбрасывается в ноль инструкциями ADD, ADDC, SUBB, MUL, и DIV. 3. Третий и четвертый биты выбирают текущий банк регистров.

4. См. описание третьего бита выше 5. F0: Пользовательский флог 0. Это адресуемый бит общего назначения который используется программой микроконтроллера. 6. AC: Флаг служебного переноса. Этот бит устанавливается в единицу если в результате арифметической операции произошел перенос или заем (сложение или вычитание) из полубайта штаршего разряда. Во всех других случаях он сбрасывется в ноль. 7. CY: Флаг переноса (Carry Flag). Этот флаг устанавливается когда последняя арифметическая операция вернула значение с переносом (сложение) или с заемом (отрицательным переносом в случае вычитания). |

C8051F340.h | ||||||||||||||||||||

| 0xD1 | REF0CN | Управление опорным напряжением | C8051F340.h | ||||||||||||||||||||

| 0xC9 | REG0CN | Управление регулятором напряжения | C8051F340.h | ||||||||||||||||||||

| 0xEF | RSTSRC | Сброс конфигурации/статуса источника | C8051F340.h | ||||||||||||||||||||

| 0xAC | SBCON1 | управление генератором скорости передачи УАПП1 (универсальный асинхронный приемопередатчик, англ. UART1) | C8051F340.h | ||||||||||||||||||||

| 0xB5 | SBRLH1 | верхний регистр генератора скорости передачи УАПП1 (универсальный асинхронный приемопередатчик, англ. UART1) | C8051F340.h | ||||||||||||||||||||

| 0xB4 | SBRLL1 | нижний регистр генератора скорости передачи УАПП1 (универсальный асинхронный приемопередатчик, англ. UART1) | C8051F340.h | ||||||||||||||||||||

| 0xD3 | SBUF1 | Буфер данных УАПП1 (универсальный асинхронный приемопередатчик, англ. UART1) | C8051F340.h | ||||||||||||||||||||

| 0xD2 | SCON1 | Управление УАПП1 (универсальный асинхронный приемопередатчик, англ. UART1) | C8051F340.h | ||||||||||||||||||||

| 0x99 | SBUF0 | Буфер данных УАПП0 (универсальный асинхронный приемопередатчик, англ. UART0) | C8051F340.h | ||||||||||||||||||||

| 0x98 | SCON0 | Управление УАПП0 (универсальный асинхронный приемопередатчик, англ. UART0) | C8051F340.h | ||||||||||||||||||||

| 0xC1 | SMB0CF | Конфигурирование системной шины (англ. SMBus) | C8051F340.h | ||||||||||||||||||||

| 0xC0 | SMB0CN | Управление системной шиной (англ. SMBus) | C8051F340.h | ||||||||||||||||||||

| 0xC2 | SMB0DAT | Данные системной шины (англ. SMBus) | C8051F340.h | ||||||||||||||||||||

| 0xE5 | SMOD1 | Режим работы УАПП1 (универсальный асинхронный приемопередатчик, англ. UART1) | C8051F340.h | ||||||||||||||||||||

| 0x81 | SP |

Указатель на стек. Данный регистр содержит в себе указатель на вершину стека. Указатель на стек инкрементируется перед каждой операцией PUSH. Значение по умолчанию и после сброса — 0x07. |

C8051F340.h | ||||||||||||||||||||

| 0xA1 | SPI0CFG | Конфигурация SPI (Serial Peripheral Interface) | C8051F340.h | ||||||||||||||||||||

| 0xA2 | SPI0CKR | Управление частотой SPI (Serial Peripheral Interface) | C8051F340.h | ||||||||||||||||||||

| 0xF8 | SPI0CN | Управление SPI0 (Serial Peripheral Interface) | C8051F340.h | ||||||||||||||||||||

| 0xA3 | SPI0DAT | Данные SPI (Serial Peripheral Interface) | C8051F340.h | ||||||||||||||||||||

| 0x88 | TCON | Управление таймером-счетчиком | C8051F340.h | ||||||||||||||||||||

| 0x8C | TH0 | Таймер-счетчик 1 верхний регистр | C8051F340.h | ||||||||||||||||||||

| 0x8D | TH1 | Таймер-счетчик 1 верхний регистр | C8051F340.h | ||||||||||||||||||||

| 0x8A | TL0 | Таймер-счетчик 0 нижний регистр | C8051F340.h | ||||||||||||||||||||

| 0x8B | TL1 | Таймер-счетчик 1 нижний регистр | C8051F340.h | ||||||||||||||||||||

| 0x89 | TMOD | Выбор режима таймера-счетчика | C8051F340.h | ||||||||||||||||||||

| 0xC8 | TMR2CN | Управление таймером-счетчиком 2 | C8051F340.h | ||||||||||||||||||||

| 0xCD | TMR2H | Верхний регистр таймера-счетчика 2 | C8051F340.h | ||||||||||||||||||||

| 0xCC | TMR2L | Нижний регистр таймера-счетчика 2 | C8051F340.h | ||||||||||||||||||||

| 0xCB | TMR2RLH | Сброс (перезагрузка) верхнего регистра таймера-счетчика 2 | C8051F340.h | ||||||||||||||||||||

| 0xCA | TMR2RLL | Сброс (перезагрузка) нижнего регистра таймера-счетчика 2 | C8051F340.h | ||||||||||||||||||||

| 0x91 | TMR3CN | Управление таймером-счетчиком номер 3 | C8051F340.h | ||||||||||||||||||||

| 0x95 | TMR3H | Верхний регистр таймера-счетчика номер 3 | C8051F340.h | ||||||||||||||||||||

| 0x94 | TMR3L | Нижний регистр таймера-счетчика номер 3 | C8051F340.h | ||||||||||||||||||||

| 0x93 | TMR3RLH | Сброс (перезагрузка) верхнего регистра таймера-счетчика номер 3 | C8051F340.h | ||||||||||||||||||||

| 0x92 | TMR3RLL | Сброс (перезагрузка) нижнего регистра таймера-счетчика номер 3 | C8051F340.h | ||||||||||||||||||||

| 0xFF | VDM0CN | мониторинг VDD | C8051F340.h | ||||||||||||||||||||

| 0x96 | USB0ADR | абстрактный (англ. Indirect — непрямой, косвенный) адресный регистр USB0 | C8051F340.h | ||||||||||||||||||||

| 0x97 | USB0DAT | регистр данных USB0 | C8051F340.h | ||||||||||||||||||||

| 0xD7 | USB0XCN | Управление приемопередатчиком USB | C8051F340.h | ||||||||||||||||||||

| 0xE1 | XBR0 | Управление коммутатором ввода-вывода 0 | C8051F340.h | ||||||||||||||||||||

| 0xE2 | XBR1 | Управление коммутатором ввода-вывода 1 | C8051F340.h | ||||||||||||||||||||

| 0xE3 | XBR2 | Управление коммутатором ввода-вывода 2 | C8051F340.h |

Обработка прерываний

[править]Ядро CIP-51 включает в себя расширенную систему обработки прерываний, которая поддерживает множественные источники прерываний и два уровня приоритетов прерываний. Распределение маркеров источников прерываний между внутренней периферией микроконтроллера и внешними входными контактами, сильно варьируется в зависимости от типа конкретного микроконтроллера. Каждому источнику прерываний назначен один или несколько флагов прерываний расположенных в регистрах специального назначения (SFR). Когда внутренний периферийный блок или внешнее устройство создаю условие возникновения прерывания, то в соответствующий флаг прерывания записывается логическая единица.

Если прерывания разрешены для данного источника прерываний, запрос прерывания генерируется сразу после установки флага прерывания. После завершения текущей инструкции процессор генерирует вызов LCALL на заранее определенный адрес, для передачи управления сервисной программе обработки прерывания (interrupt service routine, ISR). Каждая программа обработки прерываний (ISR) должна завершиться выполнением инструкции RETI, которая возобновляет выполнение основной программы с того места где произошло прерывание. Если обработка прерываний запрещена для данного источника, то прерывание игнорируется на аппаратном уровне и основная программа выполняется дальше. (Флаг прерываний устанавливается в 1 даже если прерывания запрещены.)

Обработка прерываний может быть разрешена или запрещена для каждого из источников индивидуально с помощью соответствующего бита регистра специального назначения IE-EIE2. Также можно запретить или разрешить обработку всех прерываний глобально путем установки в единицу бита-флага IE.7 регистра EA. Установка этого бита в ноль запрещает все прерывания не зависимо от индивидуальных разрешений для каждого из источников прерывания.

Некоторые флаги прерываний сбрасываются в ноль автоматически после того как процессор запускает процедуру обработки прерывания (Interrupt Service Routine, ISR). Но, большинство флагов автоматически не сбрасываются и должны быть принудительно программно сброшены перед выходом их подпрограммы обработки прерывания (ISR). Если флаг прерывания не будет сброшен до вызова инструкции "возвращения из прерывания" (return-from-interrupt, RETI), то будет немедленно сгенерирован новый запрос прерывания и процессор опять вызовет подпрограмму обработки прерывания (ISR) после выполнения текущей инструкции.

Векторы и источники прерываний

[править]Микроконтроллер поддерживает множественные источники прерываний. Прерывание может быть эмулировано программно путем установки в единицу флага прерывания. Тогда, если для данного флага разрешена обработка прерываний, будет сгенерирован запрос на прерывание и процессор направит его по адресу подпрограммы обработки прерывания данного флага. Источники прерываний, ассоциированные вектор-адреса, приоритеты, контрольные биты все приведены в таблице 9.4. Информацию о специфике прерываний для каждого из встроенных периферийных устройств можно найти в этом руководстве.

Внешние прерывания

[править]Источники внешних прерываний INT0 и INT1 могут быть сконфигурированы как активные прерывания с высоким или низким приоритетом, с срабатыванием по перепаду или по уровню (англ. edge or level edge sensitive). Биты IN0PL (обратный INT0) и IN1PL (обратный INT1) регистра IT01CF выбирают активное старшее или младшее (по приоритету) прерывание; биты IT0 и IT1 регистра TCON выбирают ограничением по уровню или по перепаду. Таблица ниже содержит все возможные конфигурации.

Привязка прерываний INT0 и INT1 к контактам портов определяется в регистре IT01CF (см. описание регистров специального назначения раздел 9.13). Заметьте, что привязка INT0 и INT1 к контактам порта не зависит от любых привязок коммутатора (Crossbar). Мониторинг привязанных к INT0 и INT1 контактов порта будет производится в обход внутренней периферии привязанной к порту через коммутатор (Crossbar). Чтобы привязать контакты портов эксклюзивно к INT0 и/или INT1 необходимо прописать "пропуски" в настройках коммутатора для этих контактов (выводов). Это производится путем установки соответствующих бит регистра XBR0 (см. раздел "15.1. Декодер приоритетов коммутатора"). Чаще всего контакты внешних прерываний исключаются из обработки коммутатором и настраиваются как выводы с открытым стоком с блокировкой (pin latch) установленной в "1".

IE0 (TCON.1) и IE1 (TCON.3) служат в качестве флагов внешних прерываний для INT0 и INT1. Если внешние прерывания INT0 и INT1 настроены как "чувствительные к перепаду" (edge-sensitive), то соответствующий флаг прерываний будет автоматически обнуляться сразу после вызова подпрограммы обработки прерывания (ISR). В случае настройки срабатываний по уровню (level sensitive), флаг прерывания сохранит свое значение битовой единицы во время обработки прерывания как определено соответствующим обратным битом (polarity bit) IN0PL или IN1PL; флаг сохраняет нулевое значение если прерывание не активно. Источник внешнего прерывания должен удерживать прерывание в активном состоянии до тех пор, пока не запрос на прерывание не будет распознан. После этого он должен деактивировать прерывание до того как будет окончено выполнение подпрограммы обработки прерывания (ISR) или другой запрос на прерывание будет сгенерирован.

Приоритеты прерываний

[править]Каждому прерыванию может быть индивидуально назначен определенный приоритетный уровень: высокий или низкий. Прерывание с более низким приоритетом может быть вытеснено прерыванием с более высоким приоритетом. прерывание с высоким приоритетом не вытесняется. Каждое прерывание имеет свой бит приоритета в регистре специального назначения IP или EIP2 служащий для задания уровня приоритета. По умолчанию всем прерываниям назначен низкий уровень приоритета. Если два запроса на прерывание будут распознаны одновременно, то первым будет вызвано прерывание с более высоким приоритетом. Если оба прерывания имеют одинаковый приоритет, то будет использовано стандартное значение приоритета, которое можно найти в таблице 9.4.

Задержки прерываний

[править]Время отклика прерывания зависит от текущего состояния процессора. Состояние и приоритет выполняемого прерывания проверяются в течении каждого такта. Поэтому, самое быстрое время отклика прерывания составляет 6 тактов: один такт на обнаружение прерывания и пять системных тактов на направление вызова LCALL подпрограмме обработки прерывания (ISR). Если прерывание выполняется при вызове инструкции RETI, выполняется дополнительная инструкция до вызова LCALL для обслуживания выполняемого прерывания. Таким образом, наибольшее время отклика прерывания (когда другие прерывания не обрабатываются или прерывание имеет наивысший приоритет) наблюдается когда процессор выполняет инструкцию RETI сразу послу выполнения инструкции DIV. В этом случае время отклика увеличивается до 20 тактов: один такт на обнаружение прерывания, шесть тактов на выполнение инструкции RETI, восемь тактов на выполнение инструкции DIV и пять системных тактов на направление вызова LCALL подпрограмме обработки прерывания (ISR). Если процессор обслуживает программу обработки прерывания с равным или более высоким приоритетом, то новое прерывание не будет отработано до завершения обработки текущего, включая инструкцию RETI и все последующие.

Заметьте, что процессор простаивает во время операция чтения/записи Flash памяти и при обращении к буферу USB (USB FIFO MOVX, см. раздел "13.2. Работа с буфером USB"). Время отклика (задержка обработки) прерывания увеличивается если процессор в данный момент простаивает. Отклик в такой ситуации определяется суммой времени на инициализацию прерывания (описано выше) и времени простоя процессора.

| Источник прерывания |

Вектор прерывания |

Приори тет |

Флаг обработки |

Поддер жка битовой адреса ции |

Автома тический аппарат ный сброс |

Флаг разрешения обработки |

Флаг приоритета |

Программная константа |

|---|---|---|---|---|---|---|---|---|

| Reset | 0x0000 | Наивысший | None | N/A | N/A | всегда разрешено |

всегда высокий |

|

| Внешнее прерывание 0 | 0x0003 | 0 | IE0 (TCON.1) | Да | Да | EX0 (IE.0) | PX0 (IP.0) | INTERRUPT_INT0 |

| Переполнение таймера 0 | 0x000B | 1 | TF0 (TCON.5) | Да | Да | ET0 (IE.1) | PT0 (IP.1) | INTERRUPT_TIMER0 |

| Внешнее прерывание 1 | 0x0013 | 2 | IE1 (TCON.3) | Да | Да | EX1 (IE.2) | PX1 (IP.2) | INTERRUPT_INT1 |

| Переполнение таймера 1 | 0x001B | 3 | TF1 (TCON.7) | Да | Да | ET1 (IE.3) | PT1 (IP.3) | INTERRUPT_TIMER1 |

| Последовательный порт 0 | 0x0023 | 4 | RI0 (SCON0.0)

TI0 (SCON0.1) |

Да | Нет | ES0 (IE.4) | PS0 (IP.4) | INTERRUPT_UART0 |

| Переполнение таймера 2 | 0x002B | 5 | TF2H (TMR2CN.7)

TF2L (TMR2CN.6) |

Да | Нет | ET2 (IE.5) | PT2 (IP.5) | INTERRUPT_TIMER2 |

| Последовательный внешний порт 0 | 0x0033 | 6 | SPIF (SPI0CN.7)

WCOL (SPI0CN.6) MODF (SPI0CN.5) RXOVRN (SPI0CN.4) |

Да | Нет | ESPI0 (IE.6) | PSPI0 (IP.6) | INTERRUPT_SPI0 |

| Интерфейс шины SMBus0 | 0x003B | 7 | SI (SMB0CN.0) | Да | Нет | ESMB0 (EIE1.0) | PSMB0 (EIP1.0) | INTERRUPT_SMBUS0 |

| Интерфейс USB | 0x0043 | 8 | Special | Нет | Нет | EUSB0 (EIE1.1) | PUSB0 (EIP1.1) | INTERRUPT_USB0 |

| Сравнение границ полосы значений (англ. Window Comparison) АЦП0 (ADC0) | 0x004B | 9 | AD0WINT (ADC0CN.3) | Да | Нет | EWADC0 (EIE1.2) | PWADC0 (EIP1.2) | INTERRUPT_ADC0_WINDOW |

| Преобразование завершено АЦП0 (ADC0) | 0x0053 | 10 | AD0INT (ADC0CN.5) | Да | Нет | EADC0 (EIE1.3) | PADC0 (EIP1.3) | INTERRUPT_ADC0_EOC |

| Программируемый счетчик-массив, ПСМ0 (Programmable Counter Array, PCA0) | 0x005B | 11 | CF (PCA0CN.7)

CCFn (PCA0CN.n) |

Да | Нет | EPCA0 (EIE1.4) | PPCA0 (EIP1.4) | INTERRUPT_PCA0 |

| Компаратор 0 | 0x0063 | 12 | CP0FIF (CPT0CN.4) CP0RIF (CPT0CN.5) | Нет | Нет | ECP0 (EIE1.5) | PCP0 (EIP1.5) | INTERRUPT_COMPARATOR0 |

| Компаратор 1 | 0x006B | 13 | CP1FIF (CPT1CN.4) CP1RIF (CPT1CN.5) | Нет | Нет | ECP1 (EIE1.6) | PCP1 (EIP1.6) | INTERRUPT_COMPARATOR1 |

| Переполнение таймера 3 | 0x0073 | 14 | TF3H (TMR3CN.7)

TF3L (TMR3CN.6) |

Нет | Нет | ET3 (EIE1.7) | PT3 (EIP1.7) | INTERRUPT_TIMER3 |

| Прерывание VBUS со срабатыванием по уровню сигнала (по установившемуся значению сигнала) | 0x007B | 15 | N/A | N/A | N/A | EVBUS (EIE2.0) | PVBUS (EIP2.0) | INTERRUPT_VBUS_LEVEL |

| Последовательный порт 1 | 0x0083 | 16 | RI1 (SCON1.0)

TI1 (SCON1.1) |

Нет | Нет | ES1 (EIE2.1) | PS1 (EIP2.1) | INTERRUPT_UART1 |

Описание регистров прерываний

[править]| Этот раздел статьи ещё не написан. Согласно замыслу одного или нескольких участников Викиучебника, на этом месте должен располагаться специальный раздел.

Вы можете помочь проекту, написав этот раздел. |

Режимы управления питанием

[править]Ядро CIP-51 поддерживает два программно управляемых режима питания: "ожидание" и "останов". Режим ожидания отключает процессор оставляя периферию и тактовые генераторы в рабочем состоянии. В режиме "останов" процессор выключен, обработка прерываний отключена, внутренний осциллятор остановлен (аналоговая периферия остается в ранее установленном состоянии; сигналы внешнего осциллятора игнорируются). Так как тактовый генератор работает в режиме ожидания, объем потребляемой энергии определяется частотой генератора и количеством внутренних периферийных блоков оставшихся в активном режиме. Режим "останов" сводит энергопотребление к минимуму. На изображении 1.15 приведены регистры контроля питания (Power Control Register, PCON) используемые для определения режимов управления питанием.

Несмотря на то, что у CIP-51 есть встроенные режимы "ожидание" и "останов" (как и любой другой система на базе архитектуры 8051), внутреннее управление питанием организовано разнообразнее за счет возможности управления тактовым генератором и отдельными периферийными блоками. Каждый аналоговый блок может быть отключен отдельно когда не используется и переведен в энергосберегающий режим. Цифровые периферийные блоки, такие как таймеры и последовательные шины, когда не используются, потребляют незначительное количество энергии. Значительное снижение потребления энергии дает отключение встроенного осциллятора, но его перезапуск требует перезагрузки всего микроконтроллера.

Встроенный осциллятор может быть переведен в режим приостановки (Suspend mode) (см. раздел "14. Осцилляторы"). В режиме приостановки осциллятор выключен до тех пор пока не будет обработано событие инициации USB, или пока сигнал на входе VBUS не совпадет по направлению (polarity) с значением в бите VBPOL регистра REG0CN (определения SFR, раздел 8.1)

Режим ожидания

[править]| Этот раздел статьи ещё не написан. Согласно замыслу одного или нескольких участников Викиучебника, на этом месте должен располагаться специальный раздел.

Вы можете помочь проекту, написав этот раздел. |

Система предварительной выборки

[править]| Этот раздел статьи ещё не написан. Согласно замыслу одного или нескольких участников Викиучебника, на этом месте должен располагаться специальный раздел.

Вы можете помочь проекту, написав этот раздел. |

Сброс (Reset)

[править]| Этот раздел статьи ещё не написан. Согласно замыслу одного или нескольких участников Викиучебника, на этом месте должен располагаться специальный раздел.

Вы можете помочь проекту, написав этот раздел. |

Flash память

[править]Перепрограммируемая энергонезависимая память Flash память служит для хранения программного кода и данных для долгосрочного хранения. Запись в Flash память производится через интерфейс C2 или внутренней программой с помощью инструкции MOVX. После обнуления бита Flash памяти он должен быть стерт перед записью в него логической единицы. Перед перепрограммированием байты Flash памяти затираются (устанавливается значение 0xFF). Для дополнительного контроля операции чтения/записи управляются аппаратно; получение подтверждения об окончании операции чтения/записи не требуется. Выполнение внутренней программы приостанавливается на время операции чтения/записи в Flash память.

Запись программы в Flash память

[править]Использование программатора от компании Silicon Labs или другого производителя, подключенного через интерфейс C2, является наиболее простым методом записи программы в Flash память. Такой способ подразумевает работу с не инициализированным устройством. Описание команд для работы с C2 интерфейсом приведено в разделе "23. C2 интерфейс".

<html> Для контроля целостности содержимого Flash памяти, строго рекомендуется оставлять задействованным VDD монитор для любой системы которая производит программную запись или стирание Flash памяти. Также важно убедится в том, что бит FLRT регистра FLSCL установлен в единицу, если в устройстве используется системная частота превышает 25 МГц. </html>

Защита от случайного стирания

[править]Запись и стирания информации из Flash памяти защищается функцией зашиты от записи (lock-and-key). Перед тем как производить указанные операции необходимо записать кодовую последовательность 0xA5, 0xF1 в специальный регистр FLKEY. Важен порядок ввода значений, интервал между кодами не имеет значения. Если будет введен не правильный код, то операции записи и стирания будут заблокированы до следующего перезапуска (сброса) устройства. Также эти операции не разрешаются без ввода ключевых кодов. Защита устанавливается повторно после каждого цикла стирания/записи; ввод ключей необходимо повторить. Регистр FLKEY описан в разделе "12.2 Определения SFR".

Форматирование Flash памяти

[править]Запись в Flash память может производится внутренней программной с использованием инструкции MOVX с адресом назначения и байтом данных в качестве параметром инструкции. Перед использованием этой инструкции для записи в Flash память, необходимо разрешить запись в Flash память: записать кодовые последовательности в регистр FLKEY (как описано выше); установить в единицу бит разрешения записи в хранилище программы (Program Store Write Enable, PSWE) — PSCTL.0 (это перенаправит инструкцию MOVX на Flash память). Значение бита PSWE не меняется пока программа явно не перезапишет его.

С помощью процедуры записи можно установить все биты Flash памяти в ноль, но нельзя отформатировать установкой во все биты логической единицы. Для форматирования используется операция стирания (erase). Любой байт перед перезаписью необходимо стереть. Пространство Flash памяти разделено на "страницы" по 512 байт. Операция стирания применяется к одной странице (устанавливая все байты в 0xFF). Для стирания всей страницы необходимо выполнить следующие шаги:

- Отключить прерывания (рекомендуется)

- Записать первый кодовый ключ в регистр FLKEY: 0xA5

- Записать второй кодовый ключ в регистр FLKEY: 0xF1

- Установить PSEE бит регистра PSCTL

- Установить PSWE бит регистра PSCTL

- Стереть побайтово содержимое страницы используя инструкцию MOVX

- Снять PSWE бит регистра PSCTL

- Снять PSEE бит регистра PSCTL

Интерфейс внешней памяти

[править]| Этот раздел статьи ещё не написан. Согласно замыслу одного или нескольких участников Викиучебника, на этом месте должен располагаться специальный раздел.

Вы можете помочь проекту, написав этот раздел. |

Генераторы частоты (осцилляторы)

[править]| Этот раздел статьи ещё не написан. Согласно замыслу одного или нескольких участников Викиучебника, на этом месте должен располагаться специальный раздел.

Вы можете помочь проекту, написав этот раздел. |

Порты ввода/вывода

[править]Цифровые и аналоговые ресурсы доступны через 40 контактов ввода/вывода (48 контактный корпус) или через 25 контактов ввода/вывода (32 контактный корпус). Порты организованы в соответствии с схемной приведенной на изображении 15.1. Каждый из контактов (выводов) порта может быть определен как аналоговый вход/выход или вход/выход общего назначения (general-purpose I/O, GPIO). Контакты P0.0-P3.7 могут быть привязаны к одному из внутренних цифровых ресурсов, как показано на изображении 15.3. Конструктор свободно вытирает какие функции назначать контактам портов ввода/вывода, ограничиваясь лишь их количеством. Такая гибкость привязки контактов обусловлена использованием коммутатора очередности (Priority Crossbar Decoder). Заметьте, что состояние любого контакта (pin) можно всегда контролировать считывая значение соответствующего регистра блокировки порта (Port latch), не зависимо от текущих настроек коммутатора.

Коммутатор привязывает выбранные внутренние цифровые ресурсы к контактам ввода/вывода с помощью декодера приоритетов (Priority Decoder) (рис. 15.3, 15.4). Регистры XBR0, XBR1 и XBR2, описанные в определениях регистров специального назначения (SFR) (см. 15.1, 15.2, 15.3), используются для выбора внутренних цифровых функций.

Все порты ввода/вывода работают с напряжением 5 В (рис. 15.2). Режим работы портов может быть установлен в регистрах режима вывода (Port Output Mode registers) (PnMDOUT, где n = 0,1,2,3,4) как двухтактный или режим с открытым стоком. Подробные электрические характеристики портов ввода/вывода приведены в таблице 15.1

-

Рис. 15.1 Функциональная блок-схема портов ввода/вывода (порт 0 через порт 3)

-

Блок-схема портов ввода/вывода

Коммутирующий декодер приоритетов

[править]Коммутирующий декодер приоритетов назначает приоритеты для всех функций ввода/вывода, начиная с UART0. Когда происходит выбор цифрового ресурса, этому ресурсу присваивается наименее значимый свободный вывод порта (исключая UART0, который всегда привязан к выводам 4 и 5). Если вывод уже занят, то коммутатор пропускает его при привязке новых ресурсов. Также будут пропущены выводы которым назначен соответствующий бит регистра PnSKIP. Регистра PnSKIP позволяет программно исключать выводы которые в последующем будут использоваться как аналоговые входы, выделенные выводы или порты общего назначения GPIO.

Важное замечание касательно настройки коммутатора: если контакт порта занят внешним устройством не теребующим использования коммутатора, то для этого контакта должен быть явно установлен бит в регистре PnSKIP. Это касается сигнального контакта VREF, контактов внешних осцилляторов (XTAL1, XTAL2), сигнального контакта начала внешнего АЦП преобразования (CNVSTR), контрольного контакта внешней памяти (EMIF), и любого используемого контакта компаратора или АЦП. Регистры PnSKIP также используются для исключения контактов которые будут использоваться как контакты ввода/вывода общего назначения (General Purpose Input/Output, GPIO). Коммутатор пропускает ранее назначенные контакты. На изображении 15.3 показаны все возможные привязки контактов к периферийным устройствам. Изображение 15.4 демонстрирует состояние коммутирующего декодера без пропусков портов. На изображении 15.5 приведен пример коммутатора с пропущенными контактами P0.2, P0.3 и P1.0.

-

Рис. 15.3 Все возможные привязки контактов к периферийным устройствам.

-

15.4 Состояние коммутирующего декодера без пропусков портов.

-

15.5 Пример коммутатора с пропущенными контактами P0.2, P0.3 и P1.0

Регистры XBR0, XBR1 и XBR2 используются для привязки цифровых ресурсов ввода/вывода к физическим контактам портов. При выборе системной шины коммутатор ассоциирует оба контакта (SDA и SCL) с системной шиной; если выбран один из УАПП (универсальный асинхронный приёмопередатчик, Universal Asynchronous Receiver/Transmitter, UART) коммутатор ассоциирует оба контакта (TX и RX) с УАПП. Для нулевого УАПП — UART0 всегда выделены фиксированные контакты для обеспечения возможности загрузки устройства; UART TX0 всегда привязан к P0.4; UART RX0 всегда привязан к P0.5. Порты можно использовать практически сразу после их привязки.

Важное замечание: последовательный синхронный периферийный интерфейс (serial peripheral interface, SPI) может функционировать в трех-проводном или черырех-проводном режимах, в зависимости от состояния бит NSSMD1-NSSMD0 регистра SPI0CN. В зависимости от выбранного режима SPI, коммутационный сигнал NSS будет или не будет привязан к контакту порта.

Инициализация портов ввода/вывода

[править]Процесс инициализации портов ввода/вывода состоит из следующих шагов:

- Выбор режима ввода (аналоговый или цифровой) для всех контактов порта, используя регистр режимов ввода PnMDIN

- Выбор режима вывода двухтактный (дискретный, push-pull) или с открытым стоком (непрерывный, open-drain), используя регистр режимов вывода PnMDOUT

- Выбрать контакты которые будут игнорироваться коммутатором, используя регистр пропуска портов PnSKIP

- Назначить контакты желаемым периферийным устройствам(XBR0, XBR1)

- Включить коммутатор (XBARE = '1')

Все контакты должны быть "прописаны" как аналоговые или цифровые. Любые контакты которые будут связаны с компараторами или блоками АЦП должны быть объявлены как аналоговые. После объявления контакта аналоговым, его автоматический контроль??? (weak pull-upШаблон:Термин), цифровой обработчик (digital driver) и цифровой приемник (digital receiver) отключаются. Это снижает энергопотребление и уменьшает уровень шумов аналогового входа. Контакты объявленные как цифровые могут продолжать использоваться аналоговой периферией, но это не рекомендуется. Для настройки контакта в качестве цифровой входа, необходимо записать ноль в соответствующий бит регистра PnMDOUT и записать логическую единицу в соответствующий регистр блокировки порта Pn.

Все аналоговые контакты должны быть явно указаны для коммутатора как игнорируемые с помощью установки соответствующих бит регистра PnSKIP. Режим ввода порта устанавливается в регистре PnMDIN, где "единица" соответствует цифровому входу, а "ноль" аналоговому. Все контакты по умолчанию (после сброса) объявлены как цифровые.

Поведение контактов ввода/вывода определяться регистром режима вывода PnMDOUT. Для каждого контакта может быть выбран один из двух режимов двухтактный (дискретный, push-pull) или с открытым стоком (непрерывный, open-drain). Назначение режима не является автоматическим и должно производится даже для цифровых ресурсов выбранных в регистре XBRn. Единственным исключением являются контакты системной шины (SDA, SCL), которые работают как непрерывные (open-drain) независимо от установок в PnMDOUT. Когда бит WEAKPUD регистра XBR1 установлен в ноль, то для включается ??? (weak pull-upШаблон:Термин) для всех портов объявленных как непрерывные (open-drain). WEAKPUD не влияет на порты объявленные как дискретные (push-pull). Кроме того, для снижения энергозатрат, "weak pull-up" выключается для портов которые выдают нулевой сигнал (driving a ‘0’).

Для обеспечения функциональности цифровых портов ввода/вывода, определенной конструкцией устройства, в регистры XBR0 и XBR1 должно быть записано соответствующее значение. Запись "единицы" в бит XBARE регистра XBR1, включает коммутатор. Пока коммутатор включен внешние контакты воспринимаются как стандартные порты ввода/вывода (в режиме ввода), не зависимо от значения регистра XBRn. Одним из свойств регистра XBRn, является способность коммутировать ввод/вывод в соответствии с таблицей приоритетов; другим способом задания приоритетов в соответствии с настройками регистра XBRn, является их назначение утилитой конфигурации (Configuration Wizard utility), в ходящей в состав среды разработки Silicon Labs IDE.

Важное замечание: коммутатор должен быть включен для использования портов P0, P1, P2 и P3 в качестве стандартных портов ввода/вывода в режиме вывода. Выходной драйвер для этих портов отключается если коммутатор выключен. Порт 4 всегда функционирует как стандартный порт общего назначения GPIO.

Порт ввода/вывода общего назначения

[править]Контакты портов не "прописанные" в коммутаторе и не используемые аналоговой периферией, могут использоваться в качестве портов ввода/вывода общего назначения. Доступ к портам 3-0 осуществляется через соответствующие регистры специального назначения (SFR), которые можно адресовать как побайтово так и побитово. Порт 4 (только в корпусе с 48-ю выводами) используется регистр специального назначения с байтовой адресацией. При записи в порт, значение записанное в регистр специального назначения (SFR) блокируется для сохранения значений данных на каждом из контактов. При чтении, возвращаются логические уровни входных контактов порта не зависимо от значения регистра XBRn (то есть, даже когда контакт привязан к другому сигналу через коммутатор, регистр порта всегда может считать значение соответствующего контакта порта ввода/вывода). Исключением является выполнение инструкций чтение-изменение-запись (read-modify-write), в контексте SFR это следующие инструкции: ANL, ORL, XRL, JBC, CPL, INC, DEC, DJNZ и MOV, CLR или SETB, при действии над одиночным битом порта SFR. Для этих инструкций, значение регистра (не контакта) читаетс, изменяется и пишется обратно в SFR.

Контроллер универсальной последовательной шины USB0

[править]Устройства семейства C8051F34x включают в себя полноценную низко-/высоко-скоростную реализацию USB для подключения периферии[1]. USB контроллер (USB0) состоит из ядра последовательного интерфейса (Serial Interface Engine, SIE), приемопередатчика USB (включая согласующие сопротивления и настраиваемые нагрузочные резисторы [pull-up resistors]), килобитный блок FIFO (First In First Out) и механизм обнаружения частоты для работы без осциллятора. Подключение дополнительных элементов не требуется. Приемопередатчик и контроллер соответствуют спе5цификации USB 2.0

Замечание: этот документ подразумевает полное понимание читателем протолкала USB. Термины и сокращения, используемые в этом документе, описаны в спецификации USB. Для понимания изложенного материала рекомендуется ознакомится с последней редакцией спецификации USB.

Адресуемые каналы

[править]Всего доступно восемь адресуемых каналов. Управляющий канал (Endpoint0) всегда работает в двунаправленном режиме ввода/вывода. Остальные каналы реализованы как три пары каналов ввода/вывода.

| Адресуемое имя пары | Потоки-каналы | USB адрес |

|---|---|---|

| Endpoint0 | Endpoint0 IN | 0x00 |

| Endpoint0 OUT | 0x00 | |

| Endpoint1 | Endpoint1 IN | 0x81 |

| Endpoint1 OUT | 0x01 | |

| Endpoint2 | Endpoint2 IN | 0x82 |

| Endpoint2 OUT | 0x02 | |

| Endpoint3 | Endpoint3 IN | 0x83 |

| Endpoint3 OUT | 0x03 |

Приемопередатчик USB

[править]Приемопередатчик USB настраивается через регистр USB0XCN (см. определения SFR 16.1). Возможности настройки и управления включают в себя включение и выключение приемопередатчика, подключение и отключение нагрузочного сопротивления и выбор скоростного режима USB. Когда бит SPEED установлен в единицу, USB0 функционирует на полной скорости, и нагрузочный резистор (если подключен) соединен с контактом D+. Иначе, USB0 функционирует на низкой скорости, и нагрузочный резистор (если подключен) соединен с контактом D-. Биты 0-4 регистра USB0XCN могут быть использованы для тестирования устройства (см. определения SFR 16.1). Нагрузочный резистор подключается только при обнаружении VBUS (см. раздел "8.2 обнаружение VBUS")

Замечание: перед включением приемопередатчика необходимо убедится в доступности тактовой частоты USB (USB clock).

Доступ к регистрам USB

[править]Доступ к регистрам контроллера USB0 перечисленых в таблице 16.2 осуществляется через два регистра специального назначения (SFR): регистр адреса USB0 — USB0ADR и регистр данных USB0 — USB0DAT. Регистр адреса определяет через какой регистр USB0 будет производится чтение/запись регистра данных (USB0DAT). См. рис. 16.2

Доступ к регистрам контроля статуса каналов осуществляется путем записи номера целевого канала в USB регистр INDEX. Сразу после записи номера канала в регистр INDEX, регистры контроля статуса привязываются к целевому каналу и становятся доступными. См. описание индексированных регистров в таблице 16.2

Замечание: перед обращением к регистрам USB необходимо убедится в доступности тактовой частоты USB (USB clock).

| Имя регистра | Адрес | Описание |

|---|---|---|

| Регистры прерываний | ||

| IN1INT | 0x02 | Флаги входных прерываний Endpoint0 и Endpoints1-3 |

| OUT1INT | 0x04 | Флаги выходных прерываний Endpoints1-3 |

| CMINT | 0x06 | Флаги общих прерываний USB |

| IN1IE | 0x07 | Включение (разрешение) входных прерываний Endpoint0 и Endpoints1-3 |

| OUT1IE | 0x09 | Включение (разрешение) выходных прерываний Endpoints1-3 |

| CMIE | 0x0B | Включение (разрешение) общих прерываний USB |

| Регистры общего назначения | ||

| FADDR | 0x00 | Функциональный адрес |

| POWER | 0x01 | Управление пританием |

| FRAMEL | 0x0C | Младший байт номера кадра |

| FRAMEH | 0x0D | Старший байт номера кадра |

| INDEX | 0x0E | Выбор канала по номеру |

| CLKREC | 0x0F | Управление временем восстановления частоты |

| FIFOn | 0x20–0x23 | Буферы FIFO для Endpoints0-3 |

| Индексированные регистры | ||

| E0CSR | 0x11 | Контроль/статус канала Endpoint0 |

| EINCSRL | Младший контроль/статус байт входного канала | |

| EINCSRH | 0x12 | Старший контроль/статус байт входного канала |

| EOUTCSRL | 0x14 | Младший контроль/статус байт выходного канала |

| EOUTCSRH | 0x15 | Старший контроль/статус байт выходного канала |

| E0CNT | 0x16 | Количество полученных байт буфера FIFO Endpoint0 |

| EOUTCNTL | Младший байт счетчика пакетов выходного канала | |

| EOUTCNTH | 0x17 | Старший байт счетчика пакетов выходного канала |

Параметры частоты шины USB

[править]USB0 поддерживает приемопередачу на "полной" или "низкой" скоростях. Скорость приемопередачи выбирается установкой бита SPEED регистра специального назначения USB0XCN. На низкой скорости частота шины USB должна составлять 6 Мгц. На полой скорости — 48 Мгц. Настройки частоты шины USB описаны в разделе "14. Осцилляторы". Частота USB0 устанавливается в регистре специального назначения CLKSEL (см. определения SFR 14.6)

Схема восстановления тактовой синхронизации использует входящий поток данных для подстройки внутреннего осциллятора; это позволяет обеспечить внутреннему осциллятору (в том числе с умножителем 4x) необходимый для USB допуск отклонения частоты. Тактовая синхронизация используется в следующих конфигурациях:

| Скорость | Частота | Вход умножителя частоты 4x |

|---|---|---|

| Full Speed | Умножитель частоты 4x | Встроенный осциллятор |

| Low Speed | Встроенный осциллятор / 2 | N/A |

В большинстве случаев в режиме низкой скорости передачи нет необходимости использовать тактовую синхронизацию. Для включения режима низкой скорости с тактовой синхронизацией, необходимо программно записать единицу в бит CRLOW.

Пошаговый режим может быть использован чтобы помочь зафиксироваться (lock) системе тактовой синхронизации при высоком уровне шума в несущей среде USB. Использование этого режима при стабильном подключении не рекомендуется.

Управление буфером FIFO

[править]В качестве буфера FIFO USB0 используются 1024 байт встроенной памяти XRAM. Эта область разделяется между каналами Endpoints0-3 как показано на рис. 16.3. Область памяти выделенная для каналов Endpoints0-3 настраивается как входящая, исходящая или комбинированная (режим разделения: половина входящей, половина исходящей).

Режим разделения буфера FIFO

[править]Область памяти выделенная для каналов Endpoints1-3 может быть установлена в режим разделения, когда старшая (верхняя) половина памяти используется входящим каналом, а младшая (нижняя) половина памяти используется исходящим каналом передачи. Например: если область памяти для канала Endpoint3 работает в режиме разделения, старшие 256 байт (от 0x0540 до 0x063F) используются входящим каналом Endpoint3 IN, а младшие 256 байт (от 0x0440 до 0x053F) используются исходящим каналом Endpoint3 OUT.

Если канал не настроен для режима разделения, то пары ввода/вывода этого канала компонуются. В этом случае пара канала может использоваться только в одном из режимов (чтение/запись) поочередно; направление канала определяется битом DIRSEL в соответствующем каналу регистре EINCSRH (см. определения SFR 16.20)

Двойная буферизация FIFO