Xilinx WebPACK ISE: различия между версиями

м Правки 80.252.155.112 (обсуждение) откачены к версии Gribozavr |

|||

| Строка 31: | Строка 31: | ||

Этапы проектирования в САПР ''WebPACK ISE''. Создание модулей исходного описания проектируемого устройства. Синтез проектов, реализуемых на базе ПЛИС семейств ''FPGA'' фирмы ''Xilinx''. Реализация проектов на базе ПЛИС семейств ''FPGA'' фирмы ''Xilinx''. Моделирование цифровых устройств. Конфигурирование и оценка потребляемой мощности цифровых устройств, проектируемых на базе ПЛИС фирмы ''Xilinx'' [1]. |

Этапы проектирования в САПР ''WebPACK ISE''. Создание модулей исходного описания проектируемого устройства. Синтез проектов, реализуемых на базе ПЛИС семейств ''FPGA'' фирмы ''Xilinx''. Реализация проектов на базе ПЛИС семейств ''FPGA'' фирмы ''Xilinx''. Моделирование цифровых устройств. Конфигурирование и оценка потребляемой мощности цифровых устройств, проектируемых на базе ПЛИС фирмы ''Xilinx'' [1]. |

||

УПЯЧКА!!!! |

|||

== WEBPACK ISE – СРЕДСТВО ПРОЕКТИРОВАНИЯ ЦИФРОВЫХ УСТРОЙСТВ == |

== WEBPACK ISE – СРЕДСТВО ПРОЕКТИРОВАНИЯ ЦИФРОВЫХ УСТРОЙСТВ == |

||

Версия от 20:03, 13 мая 2009

Авторы: ФРЕНКЕЛЬ Борис Семенович, КУЗЬМИЧ Максим Сергеевич

Программируемые логические интегральные схемы (ПЛИС) представляют собой одно из самых интересных и быстроразвивающихся направлений современной цифровой микроэлектроники. За последнее десятилетие наблюдался бурный рост рынка этих устройств и существенное улучшение их характеристик. Прогнозы в этой области на ближайшее время представляются самыми оптимистичными.

С появлением ПЛИС проектирование цифровых микросхем перестало быть уделом исключительно крупных предприятий с объёмами выпуска в десятки и сотни тысяч кристаллов. Проектирование и выпуск небольшой партии уникальных цифровых устройств стал возможен в условиях проектно-конструкторских подразделений промышленных предприятий, в исследовательских и учебных лабораториях и даже в условиях домашних радиолюбительских рабочих мест. Промышленно выпускаемые "заготовки" программируемых микросхем с электрическим программированием и автоматизированным процессом перевода схемы пользователя в последовательность импульсов программирования делают проектирование новых цифровых устройств сравнимым с разработкой программного обеспечения.

Курс лабораторных работ по дисциплине "Технические средства микропроцессорных систем", посвящённый проектированию цифровых систем на базе ПЛИС на языке VHDL, призван познакомить студентов с современной методикой проектирования микроэлектронных систем. Выполнение данных лабораторных работ поможет в получении необходимой базовой подготовки для дальнейшей работы в качестве инженера по разработке и обслуживанию современных микроэлектронных систем.

ВОПРОСЫ ДЛЯ САМОСТОЯТЕЛЬНОЙ ПОДГОТОВКИ

1. Ввести имена входов и выходов схемы с использованием типа BIT_VECTOR. 2. Составить VHDL-модель каждого из типов элементов, входящих в схему. 3. Составить иерархическое VHDL-модель схемы в целом для конкретного значения N (обычно N=4). 4. Написать тестирующую программу и провести моделирование иерархического описания, получить временную диаграмму. 5. Провести описание регулярной схемы с использованием операторов generate, generic для произвольной разрядности N. 6. Написать тестирующую программу для моделирования по способу 2 при том же значении выбранного в п. 3 параметра N. 7. Сравнить результаты моделирования по способу 1 и способу 2 (результаты должны быть одинаковыми).

Изучение ПЛИС с архитектурой FPGA

Архитектура ПЛИС фирмы Xilinx. Топология ПЛИС. Логическая таблица. Триггер. Структура конфигурируемого логического блока. Схемы для ускорения арифметических операций. Мультиплексоры в ПЛИС. Шины с тремя состояниями. ОЗУ в ПЛИС. Блоки ввода-вывода сигналов. Система синхронизации. Конфигурирование ПЛИС [2, 9, 11].

ПЛИС семейства Virtex. Особенности архитектуры. Матрица Virtex. Архитектурные особенности структурных блоков. Блочная память. Программируемая трассировочная матрица. Распределение сигналов синхронизации. Периферийное сканирование. Режимы конфигурирования кристалла. Обозначения микросхем [2, 11].

ПЛИС семейства Spartan-3. Особенности архитектуры. Матрицы Spartan-3 и Spartan-3E. Архитектурные особенности структурных блоков. Передача данных с удвоенной скоростью. Цифровое управление импедансом. Блоки умножителей. Цифровой блок управления синхронизацией (DCM). Временные параметры и обозначения микросхем [2, 5, 7, 11].

Изучение средств управления проектированием

Технология разработки систем на кристалле. Вычислительные заготовки.

Особенности языка VHDL для синтеза и анализа. Методы организации системы синхронизации. Однотактная синхронизация. Двухтактная синхронизация. Временной анализ проектов микросхем. Анализ потребляемой мощности [1, 3, 4, 9, 11].

Программное обеспечение для проектирования систем на базе ПЛИС. САПР WebPACK ISE. Система HDL-моделирования ModelSim XE Starter Edition.

Этапы проектирования в САПР WebPACK ISE. Создание модулей исходного описания проектируемого устройства. Синтез проектов, реализуемых на базе ПЛИС семейств FPGA фирмы Xilinx. Реализация проектов на базе ПЛИС семейств FPGA фирмы Xilinx. Моделирование цифровых устройств. Конфигурирование и оценка потребляемой мощности цифровых устройств, проектируемых на базе ПЛИС фирмы Xilinx [1].

WEBPACK ISE – СРЕДСТВО ПРОЕКТИРОВАНИЯ ЦИФРОВЫХ УСТРОЙСТВ

Начало работы с системой

Для запуска САПР WebPACK ISE необходимо выполнить двойной щелчок мышью на иконке, расположенной на рабочем столе:

Xilinx ISE 8.1i

Другим способом запуска является выбор в главном меню операционной системы пункта "ПУСК" → "Программы" → "Xilinx ISE 8.1i" → "Project Navigator".

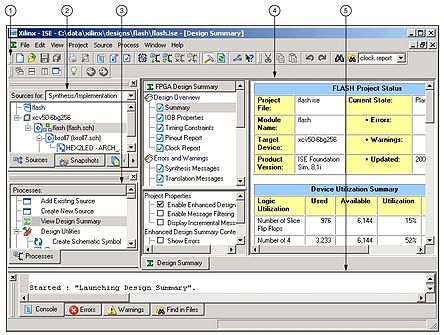

В результате будет запущен "Навигатор проекта" ("Project Navigator") – основная программа САПР WebPACK ISE. "Навигатор проекта" позволяет упорядочить файлы с исходным описанием проектируемого устройства, тестовыми модулями, модулями временных и топологических ограничений, а также предоставляет возможность простого доступа ко всем процессам, необходимым при проектировании цифрового устройства на базе ПЛИС с архитектурами FPGA и CPLD. На рисунке 1 показан внешний вид основного окна Навигатора проекта и его компоненты.

Каждому из этих этапов соответствует определённый набор процессов, к которым можно получить доступ из "Навигатора проектов".

Во время работы с САПР WebPACK ISE по всем необходимым вопросам рекомендуется обращаться к справочной системе самого ISE и сопутствующих продуктов. Для доступа к справочной системе достаточно нажать клавишу F1, что даст возможность получения контекстно-зависимой справки по выполняемой в настоящий момент задаче. Если необходимо получить доступ к определённому разделу справочной системы, то можно воспользоваться пунктом меню "Help" (рисунок 2).

При наличии подключения к Интернету из этого же раздела меню можно получить доступ к различным справочным и учебным материалам на сайте компании Xilinx (http://www.xilinx.com(англ.)), а также обновить текущую версию САПР WebPACK ISE.

Создание нового проекта

Создание описания устройства

Тестовые модули и функциональное моделирование

Использование временных ограничений

Реализация устройства на базе ПЛИС

Переразмещение проекта и проверка соответствия выводов

Проверка проекта способом временного моделирования

Загрузка конфигурации в Spartan™-3 Demo Board

ЦИФРОВАЯ СХЕМОТЕХНИКА В СИСТЕМАХ НА КРИСТАЛЛЕ

РЕКОМЕНДУЕМАЯ ЛИТЕРАТУРА

- Зотов, В.Ю. Проектирование цифровых устройств на основе ПЛИС фирмы Xilinx в САПР WebPACK ISE / В.Ю. Зотов. -- М.: Горячая линия-Телеком, 2003. -- 624 с.

- Кузелин, М.О. Современные семейства ПЛИС фирмы Xilinx: справочное пособие / М.О. Кузелин, Д.А. Кнышев, В.Ю. Зотов. -- М.: Горячая линия-Телеком, 2004. -- 440 с.

- Тарасов, И. Е. Разработка цифровых устройств на основе ПЛИС Xilinx с применением языка VHDL / И.Е. Тарасов. -- М.: Горячая линия-Телеком, 2005. -- 252 с.

- Зотов, В.Ю. Проектирование встраиваемых микропроцессорных систем на основе ПЛИС фирмы Xilinx в САПР WebPACK ISE / В.Ю. Зотов. -- М.: Горячая линия-Телеком, 2006. -- 520 с.

- Spartan-3 FPGA Family: Complete Data Sheet [Электронный ресурс] / Xilinx Inc., 2005 -- Режим доступа: http://direct.xilinx.com/bvdocs/publications/ds099.pdf(англ.). -- Яз. англ.

- Spartan-3 Starter Kit Board User Guide [Электронный ресурс] / Xilinx Inc., 2005 -- Режим доступа: http://direct.xilinx.com/bvdocs/userguides/ug130.pdf(англ.). -- Яз. англ.

- Spartan-3E FPGA Family: Complete Data Sheet [Электронный ресурс] / Xilinx Inc., 2006 -- Режим доступа: http://direct.xilinx.com/bvdocs/publications/ds312.pdf(англ.). -- Яз. англ.

- Spartan-3E Starter Kit User Guide [Электронный ресурс] / Xilinx Inc., 2006 -- Режим доступа: http://direct.xilinx.com/bvdocs/userguides/ug230.pdf(англ.). -- Яз. англ.

- Грушвицкий, Р.И. Проектирование систем на микросхемах программируемой логики / Р.И. Грушвицкий, А.Х. Мурсаев, Е.П. Угрюмов. -- СПб.: БХВ-Петербург, 2002. -- 608 с.

- Суворова, Е.А. Проектирование цифровых систем на VHDL / Е.А. Суворова, Ю.Е. Шейнин. -- СПб.: БХВ-Петербург, 2003. -- 576 с.

- Сергиенко, А.М. VHDL для проектирования вычислительных устройств / А.М. Сергиенко -- К.: ЧП "Корнейчук", ООО "ТИД ДС", 2003. -- 208 с.

- Бибило, П.Н. Основы языка VHDL / П.Н. Бибило. -- М.: СОЛОН-Р, 2002. -- 224 с.

- Бибило, П.Н. Системы моделирования интегральных схем на основе языка VHDL. StateCAD, ModelSim, LeonardoSpectrum / П.Н. Бибило. -- М.: СОЛОН Пресс, 2005. -- 384 с.

- Поляков, А.К. Языки VHDL и VERILOG в проектировании цифровой аппаратуры / А.К. Поляков. -- М.: СОЛОН-Пресс, 2003. -- 320 с.